最新要闻

- 天天热点评!中国手机市场连续5个季度暴跌 越来越多手机卖不动!为啥年轻人不换新手机了?

- 每日时讯!4G成熟 你会升5G吗?中国移动喊话不缩减5G投入:华为等中新集采大单

- 定边县冯地坑镇冯地坑村扶贫互助资金协会 天天时讯

- 在这片生态走廊,孩子们探究生物多样性…… 即时

- 万吨海上巨无霸!渤海湾首个千亿方大气田中心平台建成

- 35岁模特患厌食症去世时仅23公斤:都是为控制体重 世界播报

- 【天天速看料】首发3999元!小米电视音响5.1.4发布:200W低音炮、杜比全景声

- 当前热点-半年都不消停?你的湿疹“不一般”

- 《狂飙》片方没有为高启强报名“最佳男主角”引热议:影迷直呼可惜 到底为啥? 环球最资讯

- 林志颖车祸后再度开法拉利赛车 网友大赞心理素质真强大

- 垃圾分类全覆盖-环球聚焦

- iPhone 15系列四款机模上手:全系USB-C 接口、标配灵动岛-环球滚动

- 希荻微:子公司拟减持NVTS股票-环球热讯

- mol是什么单位等于多少毫克_mol是什么单位

- 一季度全球汽车销冠出炉:特斯拉史无前例!Model Y力压丰田卡罗拉

- 惠普战66六代上手:2.5k 120Hz屏真香|每日信息

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

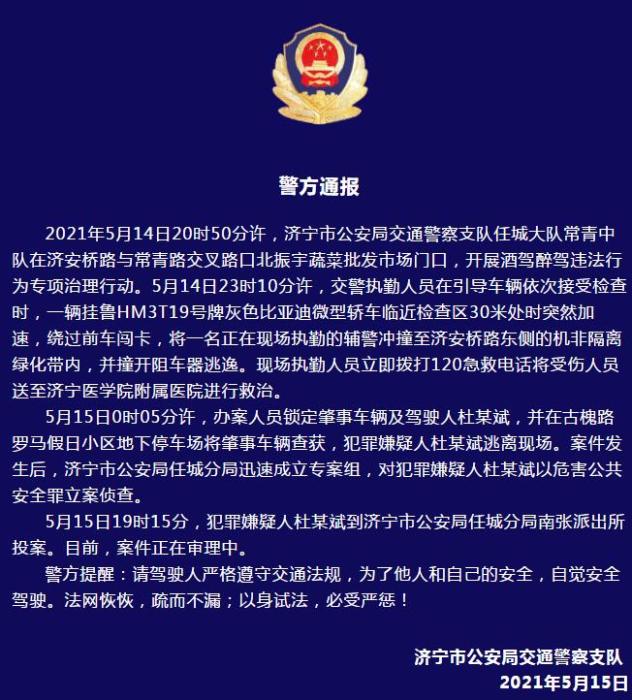

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

天天要闻:13-分频器-奇分频

(资料图片仅供参考)

(资料图片仅供参考)

1. 奇分频

实现将一个系统时钟进行 5 分频的奇数分频的功能。可以用于将高频的时钟降低为低频的时钟工作使用。

1.1 框图及波形

- 在偶数分频方法中,波形绘制时,计数器只要计数到M/2-1,计数器清零;但是在奇数分频时,不能用这样的方式(不存在1.5、2.5个周期计数)奇数分频直接计数到M(计数的最大值)

五分频时钟,计数到四,输出信号可以在0-2的时候保持低电平,3-4保持高电平,此时采用的是上升沿采样,占空比不是50%采用下降沿采样,相当于将上升沿采样的波形向左移动半个时钟周期,占空比也不是50%,不是我们想要的波形将上面的波形进行或运算,可以得到五分频时钟,编写代码的时候,上升沿和下降沿采用的波形可以作为中间变量

1.2 RTL

module divider_five( input wire sys_clk, input wire sys_rst_n, output wire clk_out ); reg [2:0] cnt; reg clk_1; reg clk_2; // 计数器变量赋值 always@(posedge sys_clk or negedge sys_rst_n) if(sys_rst_n == 1"b0) cnt <= 3"d0; else if(cnt == 3"d4) cnt <= 3"d0; else cnt <= cnt + 3"d1; // clk_1变量赋值 always@(posedge sys_clk or negedge sys_rst_n) if(sys_rst_n == 1"b0) clk_1 <= 1"b0; else if(cnt == 3"d2) clk_1 <= 1"b1; else if(cnt == 3"d4) clk_1 <= 1"b0; else clk_1 <= clk1; // clk_2变量赋值,时钟下降沿触发,需要修改敏感列表 always@(negedge sys_clk or negedge sys_rst_n) if(sys_rst_n == 1"b0) clk_2 <= 1"b0; else if(cnt == 3"d2) clk_2 <= 1"b1; else if(cnt == 3"d4) clk_2 <= 1"b0; else clk_2 <= clk1; // 输出信号 assign clk_out = clk_1 | clk2;endmodule- 创建quartus工程,添加代码,进行代码编译

1.3 Testbench

`timescale 1ns/1nsmodule tb_divider_five(); reg sys_clk; reg sys_rst_n; wire [1:0] clk_out; // 初始化时钟和复位信号 initial begin sys_clk = 1"b0; sys_rst_n = 1"b0; #20; sys_rst_n = 1"b1; end // 模拟时钟信号 always #10 sys_clk = ~sys_clk; // 模块的实例化 divider_six divider_five_inst( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .clk_out (clk_out) );endmodule- 添加仿真文件,进行仿真设置,进行仿真

1.4 优化(设置标志位)

- 在计数器最大值减一之后产生一个周期脉冲然后计数器重新开始进行计数

module divider_five( input wire sys_clk, input wire sys_rst_n, output reg clk_flag); reg [2:0] cnt; always @ (posedge sys_clk or negedge sys_rst_n) if(sys_rst_n == 1"b0) cnt <= 3"d0; else if(cnt == 3"d4) cnt <= 3"d0; else cnt <= cnt + 3"d1; always@(posedge sys_clk or negedge sys_rst_n) if(sys_rst_n == 1"b0) cnt_flag <= 1"b0; else if(cnt == 3"d3) cnt_flag <= 1"b1; else cnt_flag <= 1"b0;endmodule`timescale 1ns/1nsmodule tb_divider_five(); reg sys_clk; reg sys_rst_n; wire [2:0] clk_flag; // 初始化时钟和复位信号 initial begin sys_clk = 1"b0; sys_rst_n = 1"b0; #20; sys_rst_n = 1"b1; end // 模拟时钟信号 always #10 sys_clk = ~sys_clk; // 模块的实例化 divider_six divider_six_inst( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .clk_flag (clk_flag) );endmodule- 用两个计数器,一个由输入时钟上升沿触发,一个由输入时钟下降沿触发,最后将两个计数器的输出相或,即可得到占空比为50%的方波波形。(尽量避免将分频后时钟用作module内的后级时钟输入,但可以用于其他module的时钟输入)

- 若要实现N分频,只需在计数器计数到N-1(重新从0开始计数)时,输出分频标志即可。

关键词:

-

-

-

-

天天要闻:13-分频器-奇分频

天天热点评!中国手机市场连续5个季度暴跌 越来越多手机卖不动!为啥年轻人不换新手机了?

每日时讯!4G成熟 你会升5G吗?中国移动喊话不缩减5G投入:华为等中新集采大单

定边县冯地坑镇冯地坑村扶贫互助资金协会 天天时讯

在这片生态走廊,孩子们探究生物多样性…… 即时

环球微资讯!Go 语言 map 如何顺序读取?

全球信息:DataGridView完美解决复制粘贴功能

每日热门:【环球财经】美财长把最早债务违约日期推迟到6月5日

万吨海上巨无霸!渤海湾首个千亿方大气田中心平台建成

35岁模特患厌食症去世时仅23公斤:都是为控制体重 世界播报

【天天速看料】首发3999元!小米电视音响5.1.4发布:200W低音炮、杜比全景声

当前热点-半年都不消停?你的湿疹“不一般”

获取门禁记录方式-实时获取|世界时快讯

《狂飙》片方没有为高启强报名“最佳男主角”引热议:影迷直呼可惜 到底为啥? 环球最资讯

林志颖车祸后再度开法拉利赛车 网友大赞心理素质真强大

垃圾分类全覆盖-环球聚焦

iPhone 15系列四款机模上手:全系USB-C 接口、标配灵动岛-环球滚动

SQL进阶教程读后总结与感想|全球讯息

希荻微:子公司拟减持NVTS股票-环球热讯

mol是什么单位等于多少毫克_mol是什么单位

一季度全球汽车销冠出炉:特斯拉史无前例!Model Y力压丰田卡罗拉

惠普战66六代上手:2.5k 120Hz屏真香|每日信息

全球短讯!日本人把安卓手机做成了翻盖!极致工匠 只要100多元

2018年菲尔兹奖得主:中国这么大 需要至少50个清华-当前速递

NVIDIA市值无限逼近1万亿美元!老黄一夜赚了65亿刀 世界新消息

世界热讯:中位数怎么求_中位数

微速讯:阿扎尔换凯恩!皇马热刺重磅互换,本泽马接班人敲定,扎球王走人

世界看热讯:三亚一刑释人员砍伤2人潜逃 现已被抓获归案

2023王源演唱会重庆站直播时间+入口

证券期货业网络和数据安全实验室今日授牌 全球新资讯

乐享云南|美景·西双版纳原始森林公园

世界焦点!Node翻译i18n多语言文件,1分钟生成100种语言包

因高度计算出错 导致日本“白兔号”撞上月球摔个稀碎

著名演员罗京民老师因病去世 曾出演高分电视剧《士兵突击》

舅舅党爆料 微软Xbox将在未来推出《星空》主题限定手柄与无线耳机

育碧天猫旗舰店将于6月7号停止运营 不再经营国内的衍生品销售业务

五月天演唱会于今日晚间在鸟巢举行 不少歌迷在场外听起演唱会

湖北多地遭遇暴雨 一高校学生宿舍内居然有鱼儿出没

特斯拉或向其他制造商开放部分汽车操作系统代码 与谷歌和苹果展开竞争

米哈游《崩坏:星穹铁道》手机版全球总营收已超1亿美元 超过《原神》

印度一新郎临阵脱逃 新娘狂追到20多公里外找到新郎

路过的小学生顺手把火灭了 网友:点赞机智勇敢的小少年

环球热门:骁龙影像旗舰“百花齐放”:哪一款是你的菜?

热消息:索尼Xperia 1 V为何不用一英寸主摄?背后原因揭开

环球热消息:桌面版RTX 4060 Ti啥水平?实测表现差强人意

《英雄联盟手游今日更新4.2版本 无限火力模式正式上线

《魔戒咕噜》Steam多半差评 首日仍有800人在线受苦

高精度加法(含代码)|天天快播报

《国家水网建设规划纲要》要点速览_全球微资讯

理想L系列车型推送更新:“小主人模式”上线 通讯

【聚看点】满意率超99%!小米13 Ultra站稳高端:雷军摆庆功宴

瑞松科技因信息披露违规等违规行为被上海证券交易所采取监管措施|新动态

PC、手机生态融合!Intel、腾讯一起找到了最好的路子

AMD RX 7600公版卡小翻车:6+2针电源线插不上 全球热点

99元 联想拯救者M5鼠标上架:8000 DPI、5档调节

00后折叠男孩首次手术成功:矫正脊柱至少90度

【新要闻】真人《芭比》曝美女足部特写:暴雪高管不淡定了

神马股份: 神马股份关于向不特定对象发行可转换公司债券2023年跟踪评级结果的公告

机械硬盘可以淘汰了 梵想4TB SSD硬盘1099元(满血性能+国产闪存)|每日视点

央视曝光李鬼搬家公司:说好1700元路上疯狂加价到9000! 天天热头条

刚出生就要上绞肉机 公鸡连生存的权利都没了

全球通讯!福特CEO:超长续航电动车很难赚钱 大电池成本太高了

今日报丨7)where子句

每日消息!记录--前端小票打印、网页打印

[ESP] ESP-IDF WiFi配网(SoftAP+HTTPD)代码备注_环球看点

用好Prompt 可以让AI更智能

宕昌县南阳镇综合养老服务中心改建项目中标公示|天天观热点

日本白兔航天器月球着陆撞个稀碎 原因公布:一个错误引发惨案

资讯推荐:消除汉字“数字鸿沟”!蚂蚁“汉字拾光计划”解决生僻字输入难题

环球观速讯丨退出手机市场已有两年!LG SmartWorld服务即将停止运营

男生炫酷“海胆头”参加毕业典礼:嗨翻全场

不必过分担忧大米产需缺口 |当前速讯

获取门禁记录方式-主动获取

软件开发全部文档下载(超过三百份)

天天观天下!一文看懂GPT风口,都有哪些创业机会?

今日要闻!如何把数据从 TDengine 2.x 迁移到 3.x ?

总结Vue3 的一些知识点:Vue3 计算属性

首次10nm以下!三星研发全新4F2内存芯片:面积缩减30% 每日讯息

3199元 铭凡UM790 Pro迷你主机上架:锐龙9 7940HS_每日速讯

OneUI 5.1确认存在锁屏Bug!三星:已进行修复

成都刮起剩菜盲盒风!便宜的临期食品供不应求 焦点播报

葫芦娃救爷爷 理想ONE陷车:拖车、飞度、一串越野车来救均动弹不得|环球快播报

如何改变孩子的坏脾气教育笔记-儿童教育

海通证券联合深交所走进广西开展金融帮扶专项活动-天天头条

最全iOS 上架指南_天天视讯

天天热头条丨Spring Boot + URule 规则引擎,可视化配置太爽了!

亚马逊平台API接口是什么?-全球头条

2 分钟,搞懂 SLO 最佳实践

全网最全Kubernetes(k8s)知识点,看着一篇就够了-当前热讯

【财经分析】推动“1到100”的跨越式发展 长三角崛起生物医药产业“新基建”高地

天天快讯:缩减5G基站招标规模 大幅减少5G投资?中移动回应:外界误读

天天关注:又一个满血14GB/s!PCIe 5.0 SSD用上巨型风扇 太过分了

抗原检测盒优惠了!50人份到手19.9元

白玉兰奖入围名单揭晓 网友:正午阳光赢麻了

抛弃反人类半幅方向盘 特斯拉Cybertruck电动皮卡实车图:今年必交付 当前热门

环球要闻:渗透测试之Payload

7个工程应用中数据库性能优化经验分享

焦点热议:Prometheus笔记-告警规则配置

北京市2023年新增地方政府债务限额1117亿元

收评:沪指午后反弹涨0.35% AI赛道股发力 新能源行业低迷_天天信息