最新要闻

- 全球焦点!伯利时代首冠切尔西女足主帅:男队表现不佳,冠军献给球迷

- 售价10万以内 “电动吉姆尼”宝骏悦也内饰官图:小车也有双联屏

- 天天快消息!肉丸、鸡架超满足:东北抚顺麻辣拌6.6元/盒清仓大促

- AI孙燕姿大火!央视提醒:AI歌手翻唱或涉多项侵权行为

- 环球新动态:断轴!韩系豪华车捷尼赛思GV60上市两个月就召回

- 罕见!北方今年首轮高温来袭:山东要热成灿东了 局地39度 天天快播

- 一键斩断伸向孩子的“黑手” 36名未成年人被救助-精选

- 提速至140km/h!浙江最快高速公路来了:杭州到宁波仅1小时

- 就像买菜!男子花10万块买了8套房 最便宜一套1000元:网友感慨 天天滚动

- 遥遥领先苹果!余承东:华为WATCH4系列首发血糖评估 环球速看料

- 全国最大高铁“驾校”揭秘:16台模拟驾驶实训舱 如同开真高铁

- 全球热门:假把式!小区监控探头是粘上的,限期整改!

- 你手机装了几款APP?人均安装31个APP 年龄越小装的越多

- 摊主再回应买彩票中2574万 21人合买有钱一起赚:买一股能分百万 都分到钱

- 没人看了?美国付费有线电视用户跌至30年最低

- 如何使用多米诺骨牌作为派对主题_什么生日礼物送学生朋友最合适男生 世界简讯

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

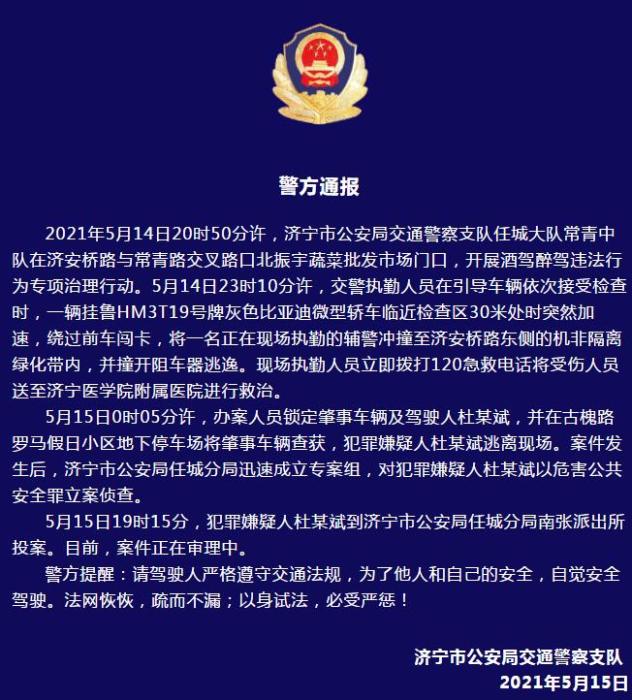

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

世界快报:序列检测器(两种设计方法和四种检测模式|verilog代码|Testbench|仿真结果)

- 一、前言

- 二、状态机法和寄存器法

- 2.1状态机法

- 2.11 使用状态机检测“1001”

- 2.12 verilog代码

- 2.13 testbench

- 2.14仿真结果

- 2.2移位寄存器法

- 2.21 使用移位寄存器法检测1001

- 2.22 verilog代码

- 2.23 testbench

- 2.24仿真结果

- 2.1状态机法

- 三、重叠检测与非重叠检测(检测序列1001)

- 3.1重叠检测

- 3.11 重叠检测方法

- 3.12verilog代码

- 3.13Testbench

- 3.14仿真结果

- 3.2非重叠检测

- 3.21 非重叠检测方法

- 3.22verilog代码

- 3.23Testbench

- 3.24仿真结果

- 3.1重叠检测

- 四、总结

数字IC经典电路设计

(相关资料图)

(相关资料图)

经典电路设计是数字IC设计里基础中的基础,盖大房子的第一部是打造结实可靠的地基,每一篇笔者都会分门别类给出设计原理、设计方法、verilog代码、Testbench、仿真波形。然而实际的数字IC设计过程中考虑的问题远多于此,通过本系列希望大家对数字IC中一些经典电路的设计有初步入门了解。能力有限,纰漏难免,欢迎大家交流指正。

快速导航链接如下:

个人主页链接

1.数字分频器设计

2.序列检测器设计

3.序列发生器设计

4.序列模三检测器设计

5.奇偶校验器设计

6.自然二进制数与格雷码转换

一、前言

在数字电路中,序列检测器(Sequence Detector)是指一种特殊类型的电路,用于寻找输入信号中一定模式的子序列。该模式可以是任意模式,包括重复模式、连续模式、间隔模式等等。通常的序列检测方法有2种:有限状态机法(FSM);移位寄存器法。

为什么需要设计序列检测电路呢?

在数字集成电路中,序列检测电路可以用于检测输入信号序列中是否存在特定的模式和序列,以及判断实际输出和理论输出是否存在差异。序列检测器是确保数字系统的正确运行不可或缺的一部分!

那么数字IC中哪些部分需要设计呢?

数字集成电路(Digital Integrated Circuit,简称DIC)中需要设计序列检测电路的部分主要包括以下几个方面:数据输入端:序列检测电路可以用于检测输入数据是否符合特定的格式要求,或者是否存在错误或干扰。在数字集成电路中,输入数据通常是通过输入端口输入的,因此需要在输入端口处设计序列检测电路。控制信号:数字集成电路中的控制信号通常是用于控制数字系统的操作序列,以确保系统按照预期的顺序执行操作。在这种情况下,序列检测电路可以用于检测控制信号是否按照预期的序列进行。数据输出端:序列检测电路还可以用于检测输出数据是否符合特定的格式要求,或者是否存在错误或干扰。在数字集成电路中,输出数据通常是通过输出端口输出的,因此需要在输出端口处设计序列检测电路。内部信号:数字集成电路中的内部信号通常是在芯片内部传递的信号,例如时钟信号、地址信号、数据信号等。在这种情况下,序列检测电路可以用于检测内部信号是否按照预期的序列进行。

在IC设计的过程中,不同的部分的序列检测器检测的序列和发挥的具体作用不尽心相同。因此在数字集成电路中,需要根据具体的应用场景,针对不同的部分设计相应的序列检测电路。

二、状态机法和寄存器法

对于序列检测器的设计,常规的设计方法有两种:状态机法和移位寄存器法。

状态机法最重要的是明白状态机状态的转移过程:在数据输入之后判断是否匹配,若匹配则进入下一状态,不匹配则根据输入的数据具体判断进入的下一状态(也有可能保持在原来的状态)。状态机设计过程一定要注重状态的数量和状态转移以及状态转移条件,避免状态的缺失以及状态转移的不合理循环。

移位寄存器法法基本原理是数据的移位和移位数据的对比:首先将对应的初始数据缓存在寄存器中作为一个数组,数据输入后置于于数组的末尾,数组其它元素左移,把最早输入的数据移出,每输入一个数据后刷新一次。然后将数组和目标序列对比,如果数组和目标序列相等,则说明出现目标序列。

2.1状态机法

2.11 使用状态机检测“1001”

题目:设计一个序列检测器,用来检测序列1001,用_状态机完成电路,可重复检测_序列1001(即本文第三部分的重叠检测)。

第一步,分析状态机状态转移,分析如下:

IDLE: 初始状态,代表目前没有接收到满足要求的数据。seq_in = 1时,等于1001中的第一个数,进入S1状态;

seq_in = 0时,保持状态。

S1:代表目前已经有了1个匹配的数据。

seq_in = 0时,当前序列为10,等于1001中的前两个数,进入S2状态;

seq_in = 1时,当前序列为11,不是1001的前两个数,但1是1001的第一个数,所以保持S1状态。

S2:代表目前已经有了2个匹配的数据。seq_in = 0时,当前序列为100,等于1001中的前三个数,进入S3状态;

seq_in = 1时,当前序列为101,不是1001的前三个数,但1是1001的第一个数,所以进入S1状态。

S3:代表目前已经有了3个匹配的数据。seq_in = 1时,当前序列为1001,与要求序列匹配,进入S4状态;

seq_in = 0时,当前序列为1000,与要求序列不配,0与初始状态匹配,所以进入IDLE状态。

S4:最终状态,代表目前已经得到了匹配的序列,输出信号翻转。seq_in = 1时,当前序列为10011,1与要求序列的第一个数匹配,所以进入S1状态;

seq_in = 0时,当前序列为10010,10与要求的前两个数匹配,所以进入S2状态。

第二步:根据流程转换分析画出状态机的状态转移图,如下图所示:

第三步:根据状态机转移图用经典三段式(或者二段式)写出verilog代码

2.12 verilog代码

//使用状态机设计检测“1001”的序列检测器//可重叠检测序列“1001”module sequence_detect01( input clk, input rst_n, input seq_in, output mismatch//检验序列是否匹配,匹配输出0,不匹配输出0 );//采用独热码编译五个状态,初始IDLE状态为待机状态//独热码相比二进制码和格雷码,方便电路设计判断、状态转移,且逻辑更简单 parameter IDLE = 5"b00001;parameter S1 = 5"b00010;parameter S2 = 5"b00100;parameter S3 = 5"b01000;parameter S4 = 5"b10000; //定义两个寄存器表示状态机的目前状态和下一状态reg [4:0] curr_state;reg [4:0] next_state;//第一段使用时序逻辑描述状态转移always@(posedge clk or negedge rst_n) begin if(!rst_n) begin curr_state <= IDLE; end else begin curr_state <= next_state; endend//第二段使用组合逻辑判断状态转移条件always@(*) begin if(!rst_n) begin next_state <= IDLE; end else begin case(curr_state) IDLE :next_state = seq_in?S1:IDLE; S1 :next_state = seq_in?S1:S2; S2 :next_state = seq_in?S1:S3; S3 :next_state = seq_in?S4:IDLE; S4 :next_state = seq_in?S1:S2; default:next_state = IDLE;//养成良好代码风格,不能遗漏,防生成latch,也可以通过赋初值避免 endcase endend//第三段描述状态输出(可以使用组合逻辑,也可以用时序逻辑)//此处采用组合逻辑,同时也提供时序逻辑代码示例assign mismatch = (curr_state ==S4) ? 1"b0 : 1"b1;//组合逻辑描述输出/*//时序逻辑描述输出always@(posedge clk or negedge rst_n) begin if(!rst_n) begin mismatch <= 1"b1; end else if(next_state == S4) begin mismatch <= 1"b0; end else begin mismatch <= 1"b1; endend*/endmodule2.13 testbench

`timescale 1ns/1ps//仿真时间单位1ns 仿真时间精度1psmodule sequence_detect01_tb();//信号申明reg clk;reg rst_n;reg seq_in;wire mismatch; //生成复位信号//为时钟信号和复位信号赋初值initial begin clk = 0; rst_n = 1; seq_in = 1; #5 rst_n = 0; #10 rst_n = 1;endalways #6 seq_in = $random;//生成随机数作为信号输入always #5 clk = ~clk;//生成时钟信号//模块实例化(将申明的信号连接起来即可)sequence_detect01 u_sequence_detect01 (.clk (clk), .rst_n (rst_n), .seq_in (seq_in), .mismatch (mismatch) );endmodule2.14仿真结果

)

Testbench中采用随机数来验证序列检测器的准确性,当时间来到705ns,随机数连续输出1001,mismatch在接收四位数字进行信号翻转。

2.2移位寄存器法

2.21 使用移位寄存器法检测1001

题目:设计一个序列检测器,用来检测序列 1001,用_移位寄存器_完成电路设计。

移位寄存器方法比较简单。设置一个和序列等长的寄存器,在数据输入后将输入移入寄存器的最低位,并判断寄存器中的值是否与序列相同。因为移位寄存器的工作原理,设计出来的序列检测器可以重叠检测序列。

2.22 verilog代码

//使用移位寄存器设计检测“1001”的序列检测器//可重叠检测序列“1001”module sequence_detect02( input clk, input rst_n, input seq_in, output regmismatch//时序逻辑中需要定义为reg型 );reg [3:0] seq_in_r;//定义一个寄存器缓存数据//使用时序逻辑完成复位和移位寄存器移位过程always@(posedge clk or negedge rst_n) begin if (!rst_n) begin seq_in_r <= 4"b0;//中间寄存器复位 end else begin seq_in_r <= {seq_in_r[2:0],seq_in};//输入数据置于数组右端,移位寄存器左移位 endend//使用时序逻辑完成复位与输出always@(posedge clk or negedge rst_n) begin if (!rst_n) begin mismatch <= 1"b1; end else if (seq_in_r == 4"b1001) begin//若检测到1001则将mismatch置1,表明检测到序列1001 mismatch <= 1"b0; end else begin mismatch <= 1"b1;//养成良好代码风格,不能遗漏,防生成latch,可通过赋初值避免 end endendmodule2.23 testbench

`timescale 1ns/1ps//仿真时间单位1ns 仿真时间精度1psmodule sequence_detect02_tb;//信号申明regclk;reg rst_n;regseq_in;wire mismatch; //复位信号生成//时钟信号与复位信号赋初值initial begin clk = 0; rst_n = 1; seq_in = 1; #5 rst_n = 0; #10 rst_n = 1;endalways #6 seq_in = $random;//生成随机数作为信号输入always #5 clk = ~clk;//生成时钟信号//模块实例化(将申明的信号连接起来即可)sequence_detect01 u_sequence_detect01 (.clk (clk), .rst_n (rst_n), .seq_in (seq_in), .mismatch (mismatch) );endmodule2.24仿真结果

Testbench中采用随机数来验证序列检测器的准确性,当时间来到705ns,随机数连续输出1001,mismatch在接收四位数字且在时钟上升沿进行信号翻转。

三、重叠检测与非重叠检测(检测序列1001)

数字IC序列检测中的重叠检测和非重叠检测是两种不同的检测方式。重叠检测是指在一个序列中,子序列之间会有部分重叠的情况,而重叠区域也需要进行检测,并被判定为单独的子序列。非重叠检测则是指在一个序列中,每个子序列之间没有重叠部分,因此只需要检测每个子序列本身是否满足特定的条件即可。

3.1重叠检测

3.11 重叠检测方法

题目:设计一个序列检测器,用来检测序列 1001,用_状态机完成电路,可重复检测_序列1001

第一步,分析状态机状态转移,分析如下:

IDLE: 初始状态,代表目前没有接收到满足要求的数据。seq_in = 1时,等于1001中的第一个数,进入S1状态;

seq_in = 0时,保持状态。

S1:代表目前已经有了1个匹配的数据。

seq_in = 0时,当前序列为10,等于1001中的前两个数,进入S2状态;

seq_in = 1时,当前序列为11,不是1001的前两个数,但1是1001的第一个数,所以保持S1状态。

S2:代表目前已经有了2个匹配的数据。seq_in = 0时,当前序列为100,等于1001中的前三个数,进入S3状态;

seq_in = 1时,当前序列为101,不是1001的前三个数,但1是1001的第一个数,所以进入S1状态。

S3:代表目前已经有了3个匹配的数据。seq_in = 1时,当前序列为1001,与要求序列匹配,进入S4状态;

seq_in = 0时,当前序列为1000,与要求序列不配,0与初始状态匹配,所以进入IDLE状态。

S4:最终状态,代表目前已经得到了匹配的序列,输出信号翻转。seq_in = 1时,当前序列为10011,1与要求序列的第一个数匹配,所以进入S1状态;

seq_in = 0时,当前序列为10010,10与要求的前两个数匹配,所以进入S2状态。

第二步:根据流程转换分析画出状态机的状态转移图,如下图所示:

第三步:根据状态机转移图用经典三段式(或者二段式)写出verilog代码

3.12verilog代码

//使用状态机设计检测“1001”的序列检测器//可重叠检测序列“1001”module sequence_detect03( inputclk , inputrst_n, inputseq_in, output reg mismatch//检验序列是否匹配,匹配输出0,不匹配输出0 );//采用独热码编译五个状态,初始IDLE状态为待机状态//独热码相比二进制码和格雷码,方便电路设计判断、状态转移,且逻辑更简单 parameterIDLE = 5"b00001;parameter S1 = 5"b00010;parameter S2 = 5"b00100;parameter S3 = 5"b01000;parameter S4 = 5"b10000;//定义两个寄存器表示状态机的目前状态和下一状态reg [4:0] curr_state;reg [4:0] next_state;//第一段使用时序逻辑描述状态转移always@(posedge clk or negedge rst_n) begin if(!rst_n) begin curr_state <= IDLE; end else begin curr_state <= next_state; endend//第二段使用组合逻辑判断状态转移条件always@(*) begin if(!rst_n) begin next_state <= IDLE; end else begin case(curr_state) IDLE :next_state = seq_in?S1:IDLE; S1 :next_state = seq_in?S1:S2; S2 :next_state = seq_in?S1:S3; S3 :next_state = seq_in?S4:IDLE; S4 :next_state = seq_in?S1:S2; default:next_state = IDLE;//养成良好代码风格,不能遗漏,防生成latch,也可以通过赋初值避免endcase endend//第三段描述状态输出(可以使用组合逻辑,也可以用时序逻辑)//此处采用时序逻辑,同时也提供组合逻辑代码示例always@(posedge clk or negedge rst_n) begin//时序逻辑描述输出 if(!rst_n) begin mismatch <= 1"b1; end else if(next_state == S4) begin mismatch <= 1"b0; end else begin mismatch <= 1"b1; endend//assign mismatch = (curr_state ==S4) ? 1"b0 : 1"b1;//组合逻辑描述输出endmodule3.13Testbench

`timescale 1ns/1ps//仿真时间单位1ns 仿真时间精度1psmodule sequence_detect03_tb();//信号申明regclk;regrst_n;regseq_in;wiremismatch;//复位信号生成//输入信号生成,输入信号为“1001001001001”//时钟信号与复位信号赋初值initial begin clk = 0; rst_n = 1; #5 rst_n = 0; #10 rst_n = 1; seq_in = 1;#10; seq_in = 0;#10; seq_in = 0;#10; seq_in = 1;#10; seq_in = 0;#10; seq_in = 0;#10; seq_in = 1;#10; seq_in = 0;#10; seq_in = 0;#10; seq_in = 1;#10; seq_in = 0;#10; seq_in = 0;#10; seq_in = 1;#10;end //时钟信号生成always #5 clk = ~clk;//模块实例化(将申明的信号连接起来即可)sequence_detect03 u_sequence_detect03( .clk(clk), .rst_n(rst_n), .seq_in(seq_in), .mismatch(mismatch) );endmodule3.14仿真结果

输入序列1001001001001,根据可重复检测理论上可检测四次信号翻转,从仿真结果可以看到mismatch发生四次翻转,且第二次翻转的1001中的第一个1来自第一组1001中最后一个1,即发生重叠亦可检测。

3.2非重叠检测

3.21 非重叠检测方法

题目:设计一个序列检测器,用来检测序列 1001,用状态机完成电路,可重复检测序列1001

第一步,分析状态机状态转移,分析如下:

IDLE: 初始状态,代表目前没有接收到满足要求的数据。seq_in = 1时,等于1001中的第一个数,进入S1状态;

seq_in = 0时,保持状态。

S1:代表目前已经有了1个匹配的数据。

seq_in = 0时,当前序列为10,等于1001中的前两个数,进入S2状态;

seq_in = 1时,当前序列为11,不是1001的前两个数,但1是1001的第一个数,所以保持S1状态。

S2:代表目前已经有了2个匹配的数据。seq_in = 0时,当前序列为100,等于1001中的前三个数,进入S3状态;

seq_in = 1时,当前序列为101,不是1001的前三个数,但1是1001的第一个数,所以进入S1状态。

S3:代表目前已经有了3个匹配的数据。seq_in = 1时,当前序列为1001,与要求序列匹配,进入S4状态;

seq_in = 0时,当前序列为1000,与要求序列不配,0与初始状态匹配,所以进入IDLE状态。

S4:最终状态,代表目前已经得到了匹配的序列,输出信号翻转。seq_in = 1时,当前序列为10011,1与要求序列的第一个数匹配,所以进入S1状态;

seq_in = 0时,当前序列为10010,10与要求的前两个数匹配,但是要求非重叠检测,所以进入IDLE状态。

第二步:根据流程转换分析画出状态机的状态转移图,如下图所示

第三步:根据状态机转移图用经典三段式(或者二段式)写出verilog代码

3.22verilog代码

//使用状态机设计检测“1001”的序列检测器//非重叠检测序列“1001”module sequence_detect04( inputclk , inputrst_n, inputseq_in, output reg mismatch//检验序列是否匹配,匹配输出0,不匹配输出0 );//采用独热码编译五个状态,初始IDLE状态为待机状态//独热码相比二进制码和格雷码,方便电路设计判断、状态转移,且逻辑更简单 parameter IDLE = 5"b00001;parameter S1 = 5"b00010;parameter S2 = 5"b00100;parameter S3 = 5"b01000;parameter S4 = 5"b10000;//定义两个寄存器表示状态机的目前状态和下一状态reg [4:0] curr_state;reg [4:0] next_state;//第一段使用时序逻辑描述状态转移always@(posedge clk or negedge rst_n) begin if(!rst_n) begin curr_state <= IDLE; end else begin curr_state <= next_state; endend//第二段使用组合逻辑判断状态转移条件always@(*) begin if(!rst_n) begin next_state <= IDLE; end else begin case(curr_state) IDLE :next_state = seq_in?S1:IDLE; S1 :next_state = seq_in?S1:S2; S2 :next_state = seq_in?S1:S3; S3 :next_state = seq_in?S4:IDLE; S4 :next_state = seq_in?S1:IDLE; default:next_state = IDLE;//养成良好代码风格,不能遗漏,防生成latch,也可以通过赋初值避免endcase endend//第三段描述状态输出(可以使用组合逻辑,也可以用时序逻辑)//此处采用时序逻辑,同时也提供组合逻辑代码示例always@(posedge clk or negedge rst_n) begin//时序逻辑描述输出 if(!rst_n) begin mismatch <= 1"b1; end else if(next_state == S4) begin mismatch <= 1"b0; end else begin mismatch <= 1"b1; endend//assign mismatch = (curr_state ==S4) ? 1"b0 : 1"b1;//组合逻辑描述输出endmodule3.23Testbench

`timescale 1ns/1ps//仿真时间单位1ns 仿真时间精度1psmodule sequence_detect04_tb();//信号申明regclk;regrst_n;regseq_in;wiremismatch;//复位信号生成//输入信号生成,输入信号为“1001001001001”//时钟信号与复位信号赋初值initial begin clk = 0; rst_n = 1; #5 rst_n = 0; #10 rst_n = 1; seq_in = 1;#10; seq_in = 0;#10; seq_in = 0;#10; seq_in = 1;#10; seq_in = 0;#10; seq_in = 0;#10; seq_in = 1;#10; seq_in = 0;#10; seq_in = 0;#10; seq_in = 1;#10; seq_in = 0;#10; seq_in = 0;#10; seq_in = 1;#10;end //时钟信号生成always #5 clk = ~clk;//模块实例化(将申明的信号连接起来即可)sequence_detect04 u_sequence_detect04( .clk(clk), .rst_n(rst_n), .seq_in(seq_in), .mismatch(mismatch) );endmodule3.24仿真结果

输入序列1001001001001,根据可不重叠检测理论上可检测两次信号翻转,从仿真结果可以看到mismatch发生两次翻转,且第二组的1001中的第一个1来自第一组1001中最后一个1,即发生重叠不可检测,所以相比于重叠检测少了第二次翻转(同理第四次翻转同样不可发生)。

四、总结

状态机法序列检测器:一句话概括就是设计复杂、不易扩展但是检测模式灵活。相比使用移位寄存器来说的话,状态机稍稍复杂些,主要体现在不易扩展(重新检测不同序列需重新设计状态转移)和状态机的状态转移判断上;但是这样也给状态机带来了优点 ,就是灵活性好,可以灵活处理输入和输出,因为状态机具有可编程性。同时可以处理较为复杂的序列检测任务,因为状态机可以支持多个状态和转换。移位寄存器法:一句话概括就是设计简单、易于扩展但是检测模式呆板。相比于使用状态机来说的话,只能处理简单的序列检测任务,因为它没有状态机的多状态和转换功能。且输入和输出的灵活性差,因为寄存器序列移位寄存器是固定的,检测模式固定。但是优势很明显,就是设计和开发相对简单,只需要几个寄存器和逻辑门。且易于扩展,如果要检测另一个序列,只需要修改输入数据。模式选择:前言部分提到了检测模式包括重叠模式、连续模式、间隔模式等等。本文着重分析重叠与非重叠检测模式,结论是重叠检测模式可以用状态机和移位寄存器设计,非重叠检测模式可以用灵活的状态机设计;本文都是基于默认的连续检测模式设计,如果采用间隔检测模式,处理方法是添加指示信号使能端,可以用状态机和移位寄存器设计。因为设计逻辑简单,所以这部分省略,可自行参照第二部分代码设计。

综上所述,状态机序列检测器适用于处理较为复杂的序列检测任务,而寄存器序列移位寄存器适用于处理简单的序列检测任务。在实际应用中,应根据具体的需求来选择合适的序列检测方法。

不定期检查、补充、纠错,欢迎随时交流纠错

最后修改日期:2023.4.22

软件版本:

仿真软件:Modelsim 10.6c

绘图软件:亿图图示

描述语言:verilog

关键词:

-

世界快报:序列检测器(两种设计方法和四种检测模式|verilog代码|Testbench|仿真结果)

数字IC经典电路设计经典电路设计是数字IC设计里基础中的基础,盖大房子的第一部是打造结实可靠的地基,每一

来源: -

-

-

世界快报:序列检测器(两种设计方法和四种检测模式|verilog代码|Testbench|仿真结果)

天天热资讯!Linux文件查找命令之locate与find

从3s到25ms!看看京东的接口优化技巧,确实很优雅!! 当前速递

碳酸锂市价止跌急涨 需求兑现仍需时日 全球速递

全球焦点!伯利时代首冠切尔西女足主帅:男队表现不佳,冠军献给球迷

售价10万以内 “电动吉姆尼”宝骏悦也内饰官图:小车也有双联屏

天天快消息!肉丸、鸡架超满足:东北抚顺麻辣拌6.6元/盒清仓大促

AI孙燕姿大火!央视提醒:AI歌手翻唱或涉多项侵权行为

环球新动态:断轴!韩系豪华车捷尼赛思GV60上市两个月就召回

罕见!北方今年首轮高温来袭:山东要热成灿东了 局地39度 天天快播

java~"与运算"实现保留一个数的低8位 速看

一键斩断伸向孩子的“黑手” 36名未成年人被救助-精选

提速至140km/h!浙江最快高速公路来了:杭州到宁波仅1小时

就像买菜!男子花10万块买了8套房 最便宜一套1000元:网友感慨 天天滚动

遥遥领先苹果!余承东:华为WATCH4系列首发血糖评估 环球速看料

全国最大高铁“驾校”揭秘:16台模拟驾驶实训舱 如同开真高铁

全球热门:假把式!小区监控探头是粘上的,限期整改!

两类存款利率加点上限调整今起执行 部分中小银行迅速行动

你手机装了几款APP?人均安装31个APP 年龄越小装的越多

摊主再回应买彩票中2574万 21人合买有钱一起赚:买一股能分百万 都分到钱

没人看了?美国付费有线电视用户跌至30年最低

如何使用多米诺骨牌作为派对主题_什么生日礼物送学生朋友最合适男生 世界简讯

读SQL进阶教程笔记16_SQL优化让SQL飞起来

一万的票隔壁唱了九千八 粉丝吐槽听不清:盖过周杰伦声音 环球要闻

热点在线丨险遭退市 老牌日化企业广州浪奇突然宣布不再卖洗衣粉

多地出手严控老年代步车 全面封杀“老头乐”:网友吵翻 你支持谁?

当前关注:电饭煲内胆是什么材质 电饭煲内胆材质说明【详解】

全球热议:问题:Duplicate报错RMAN-03009, ORA-17628, ORA-19505

解决vmware虚拟机中的linux系统新增硬盘后无法启动

【C++】在使用PImpl技术时,template/typename的不常见用法 环球速看

南京芯视界发布新一代3D dToF芯片 性能远超索尼!

HTC又要出新手机了!但我建议 还是别出来丢人了

印度发现1.5米白化眼镜蛇:一般活不过24小时 但它不一样

天天微动态丨所有熊猫都是天生近视!有的生下来就800度?

瑞士德语文学专辑_关于瑞士德语文学专辑介绍

全球最新:JDG零封BLG 水晶哥:ELK暴毙次数太多了啊!回来吧我的小枣!

LitCTF crypto wp

世界速讯:监听容器中的文件系统事件

第139篇:微信小程序的登录流程|天天讯息

环球速看:EF命令行工具 migrate.exe 进行Code First更新数据库,6.3+使用ef6.exe

4月皮卡销量排名出炉 长城江淮大增 新能源有待突破|世界时快讯

20230514学习笔记——将代码提交到码云中 天天要闻

当前速递!【LeetCode字符串#extra】KMP巩固练习:旋转字符串、字符串轮转

世界之最大全100条_世界之最大全

大模型三大能力超越ChatGPT 千亿AI巨头科大讯飞否认做手机

大爷买二等座票带孙女坐一等座被赶 12306回应:不允许乱坐 全球热点

观点:一起来学rust|简单的mingrep

关于Kubernetes-v1.23.6-网络组件-calico的安装部署...|焦点快看

【焦点热闻】好莱坞编剧大罢工:GPT技术引发激烈争议

经典28定律?苹果在中国手机市场份额2成 赚走8成利润|每日简讯

电池只能充电500次?别太荒谬!收下这份真正的充电秘籍

【全球新要闻】摊主买彩票中2千多万激动砸摊位:称21人合买 明天就分钱

CentOS7搭建keepalived+DRBD+NFS高可用共享存储

每日精选:惠普打印机禁用非原装墨盒:官方称是为用户安全考虑

当前焦点!地狱笑话?大学母亲节配图是《进击的巨人》

泥鳅汤做法_泥鳅汤的烹饪方法 环球实时

已在轨生活160多天 航天员费俊龙从太空发回对母亲的节日祝福

热播电视剧将本科写成大专 高校不干了 官方道歉|天天聚看点

【热闻】首发紫光展锐T750!海信悄然推出F70 Lite手机

迭部县气象台发布大风蓝色预警信号【2023-05-14】

three.js 入门学习(二) 环球热资讯

DIY技巧:微星B760主板13600K降压教程 CPU温度暴降25℃

世界消息!专家称电动车要发展农村型号:支持反向充电 可增加收入

环球热门:1-2!“全校班”广州队又输了!3连败+开局5轮不胜,直冲降级区

基于SLAM系统建图仿真,完成定位仿真

天天观速讯丨安卓一年一迭代谷歌也累了:开始挤牙膏更新

女子把变心男友送的黄金卖了14万:没真心但有真金!自愿赠与或不用返还_天天快看

升级彩超5项:瑞慈体检套餐279元母亲节大促 今日热搜

久穿不易变形 放克220g宽松短袖29元大促

徐工四款新“国货之光”问世:百变狮王、自动灭火机器人 国产化率100% 世界观焦点

万胜智能: 关于使用部分闲置募集资金进行现金管理的进展公告

美团一面:Spring Cloud 如何构建动态线程池?

动态焦点:每天走路超这一步数 能大幅降低死亡率 上班族学起来

B站“离谱”专利获批:开车也能发弹幕了?|新要闻

热议:俄媒:泽连斯基拒绝教皇方济各调解俄乌提议

世界热议:我对IdentityServer4的初步了解

每日关注!JavaSE面试题【长期更新】

想玩《塞尔达传说:王国之泪》却不知道买哪款Switch?这篇选购攻略帮你避坑!

CPU散片学问大:碰见这两个型号千万别买|今日热搜

01-Linux命令和C语言基础|全球快讯

全球今亮点!西湖5平米商亭租金284万 每天约7780元引热议

母亲节 我来讲一个给妈妈换了“苹果全家桶”后的故事

首次发现!唾液含剧毒的五爪金龙现身云南:寿命长达150年

每日短讯:2023年5月14日融雪剂价格最新行情预测

国金证券:稳增长政策效果加速显现 居民消费修复延续性较强

D加密沦陷!黑客放出《生化危机4重制版》破解资源:好评如潮大作免费玩

AI起了反效果:4月微软Bing市场份额不升反降

特斯拉雨天高速失控!旋转、掉头、撞墙后 司机接着加速跑了

【报资讯】怀旧服磨刀石是什么专业制作的(怀旧服磨刀石)

前端语言串讲 | 青训营笔记

女子夜里打出租 全程直播监控!司机:不自信了_当前焦点

环球快资讯丨最后一道封印解除!ChatGPT重大升级 上线联网功能

检察院不批捕取保候审后还会收监吗|世界快播

女子旅游后高烧不退确诊“不死癌症” 医生:晒太阳是重要诱因

性能完全不达标 EPA报告:特斯拉4680电池能量密度比2170还低 当前观察

landrover是什么车多少钱一辆 landrover是什么车

Python学习之六_同时访问Oracle和Mysql的方法

上海张江全链条发力营造更优企业创新发展环境 今日快讯

放弃ZEKU自研芯片!OPPO张璇:产品生命周期软件维护不受影响_世界速读

江苏扬州:体育嘉年华嗨出狂欢味 百余场赛事活动贯穿全年-全球播资讯