最新要闻

- 天天通讯!伊朗外长:伊沙恢复外交关系将为两国和地区发展注入巨大动能

- 世界快讯:日系车掀起买一送一热潮:买皓影插混送飞度、买日产楼兰送轩逸

- 天天热资讯!50万以内最舒适二排 理想L7正式交付:31.98万起售

- 环球新资讯:10年分红1000多亿!董明珠鼓励员工“砸锅卖铁”买格力股票

- 资讯推荐:全球最强!传音发布260W有线、110无线快充:8分钟充满

- 世界观热点:美国科学家改变人类科技、终极能源即将实现?真相来了!

- 世界快讯:《原子之心》更新:添加FOV设置、删除种族主义动画

- 今亮点!霸道女总裁加盟《碟中谍8》

- 天天播报:00后男生每天下班后卖烤肠解压 50元投资日赚200元:厌恶刷视频、打游戏

- 环球微速讯:比进口价格便宜!海南三亚榴莲今年6月将大规模上市

- 当废物挺好?委员称年轻人想躺平更多是调侃 奋斗的是大多数

- 天天亮点!中国足彩网竞彩11日推荐:曼城取胜无悬念

- 当前播报:amusements

- 环球热议:6月上映!《变形金刚7》角色海报发布:擎天柱、猩猩队长亮相

- 【速看料】降价潮席卷全国 车企尽数参战是为何?乘联会解答:国六B要来了

- 环球今热点:真正油电同价!比亚迪投放“深水炸弹”:13.4万买宋Pro DM-i超级混动

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

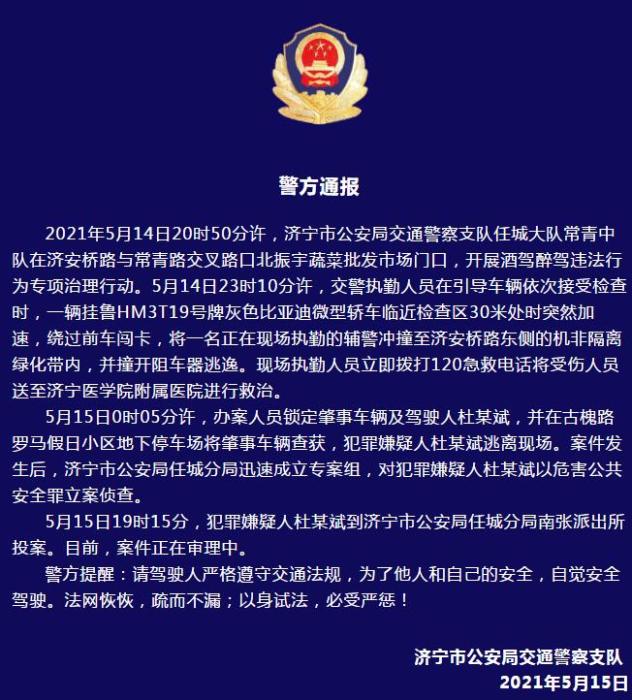

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

【世界新要闻】四位计数器testbench的设计

简单介绍一下四位计数器所要满足的条件:

1.4bit循环计数;

1,2,3,4,5,6,7,8,9,a,b,c,d,e,f,1,.......

2.能同步清零;

(资料图片)

(资料图片)

高电平有效

3.有加载功能;

高电平加载

4.优先级:清零信号 > 加载信号;

给出计数器的设计代码:

1 module count4(clk, reset, clr, ld, init, out); 2 3 input clk, reset; 4 input clr; 5 input ld; 6 input [3:0] init; 7 output [3:0] out; 8 reg [3:0] out; 9 10 always @(posedge clk or posedge reset)11 begin if(reset)12 out <= 0;13 else if(clr)14 out <= 0;15 else if(ld)16 out <= init;17 else18 out <= out+1;19 end20 endmodule

计数器的testbench设计:

对clr信号进行验证:

1. 一个周期;

2.二个周期(多个周期);

3.毛刺

1 `timescale 1ns/1ns 2 3 module tb_a; 4 5 parameter CYCLE=10; 6 7 reg clk; 8 reg reset; 9 reg clr;10 reg ld;11 reg[3:0] init;12 wire[3:0] out;13 14 //RTL instance15 count4 count4(16 .clk(clk),17 .reset(reset),18 .ld(ld),19 .init(init),20 .clr(clr),21 .out(out)22 );23 24 //generate input-clk25 initial begin26 clk=0;27 forever begin28 #(CYCLE/2);29 clk=1;30 #(CYCLE/2);31 clk=0;32 end33 end34 35 initial begin36 reset=1;37 #(5*CYCLE);38 reset=0;39 end40 41 initial begin42 clr=0;43 ld=0;44 init=0;45 #(6*CYCLE);46 47 48 49 @(negedge clk);50 51 clr=1;52 ld=0; 53 init=0; 54 #(CYCLE);55 56 @(negedge clk);57 clr=0;58 ld=0;59 init=0;60 #(5*CYCLE);61 62 @(negedge clk);63 clr=1;64 ld=0;65 init=0;66 #(2*CYCLE);67 68 @(negedge clk);69 clr=0;70 ld=0;71 init=0;72 #(5*CYCLE);73 74 @(negedge clk)75 clr=1;76 ld=0;77 init=0;78 #(CYCLE/8);79 80 81 clr=0;82 ld=0;83 init=0;84 #(20*CYCLE);85 86 $finish;87 88 89 end90 91 endmodule

波形图:

对ld加载信号进行验证:

1. 一个周期;

2.二个周期(多个周期);

3.毛刺

注意:写在一个initial块里面;

测试ld信号时,clr信号为0.

testbench:

1 `timescale 1ns/1ns 2 3 module tb_a; 4 5 parameter CYCLE=10; 6 7 reg clk; 8 reg reset; 9 reg clr; 10 reg ld; 11 reg[3:0] init; 12 wire[3:0] out; 13 14 //RTL instance 15 count4 count4( 16 .clk(clk), 17 .reset(reset), 18 .ld(ld), 19 .init(init), 20 .clr(clr), 21 .out(out) 22 ); 23 24 //generate input-clk 25 initial begin 26 clk=0; 27 forever begin 28 #(CYCLE/2); 29 clk=1; 30 #(CYCLE/2); 31 clk=0; 32 end 33 end 34 35 initial begin 36 reset=1; 37 #(5*CYCLE); 38 reset=0; 39 end 40 41 initial begin 42 clr=0; 43 ld=0; 44 init=0; 45 #(6*CYCLE); 46 47 48 49 @(negedge clk); 50 51 clr=1; 52 ld=0; 53 init=0; 54 #(CYCLE); 55 56 @(negedge clk); 57 clr=0; 58 ld=0; 59 init=0; 60 #(5*CYCLE); 61 62 @(negedge clk); 63 clr=1; 64 ld=0; 65 init=0; 66 #(2*CYCLE); 67 68 @(negedge clk); 69 clr=0; 70 ld=0; 71 init=0; 72 #(5*CYCLE); 73 74 @(negedge clk) 75 clr=1; 76 ld=0; 77 init=0; 78 #(CYCLE/8); 79 80 81 clr=0; 82 ld=0; 83 init=0; 84 #(10*CYCLE); 85 //clr_testbench 86 @(negedge clk); 87 clr=0; 88 ld=1; 89 init=5; 90 #(CYCLE); 91 92 clr=0; 93 ld=0; 94 init=0; 95 #(2*CYCLE); 96 97 @(negedge clk); 98 clr=0; 99 ld=1;100 init=5;101 #(2*CYCLE);102 103 clr=0;104 ld=0;105 init=0;106 #(2*CYCLE);107 108 @(negedge clk);109 clr=0;110 ld=1;111 init=5;112 #(CYCLE/8);113 114 clr=0;115 ld=0;116 init=0;117 #(10*CYCLE);118 119 $finish;120 121 122 end123 124 endmodule

波形图:

对计数器功能进行验证:

1. 极值测试(最大值,最小值);

2.优先级测试;

testbench:

1 `timescale 1ns/1ns 2 3 module tb_a; 4 5 parameter CYCLE=10; 6 7 reg clk; 8 reg reset; 9 reg clr; 10 reg ld; 11 reg[3:0] init; 12 wire[3:0] out; 13 14 //RTL instance 15 count4 count4( 16 .clk(clk), 17 .reset(reset), 18 .ld(ld), 19 .init(init), 20 .clr(clr), 21 .out(out) 22 ); 23 24 //generate input-clk 25 initial begin 26 clk=0; 27 forever begin 28 #(CYCLE/2); 29 clk=1; 30 #(CYCLE/2); 31 clk=0; 32 end 33 end 34 35 initial begin 36 reset=1; 37 #(5*CYCLE); 38 reset=0; 39 end 40 41 initial begin 42 clr=0; 43 ld=0; 44 init=0; 45 #(6*CYCLE); 46 47 48 49 @(negedge clk); 50 51 clr=1; 52 ld=0; 53 init=0; 54 #(CYCLE); 55 56 @(negedge clk); 57 clr=0; 58 ld=0; 59 init=0; 60 #(5*CYCLE); 61 62 @(negedge clk); 63 clr=1; 64 ld=0; 65 init=0; 66 #(2*CYCLE); 67 68 @(negedge clk); 69 clr=0; 70 ld=0; 71 init=0; 72 #(5*CYCLE); 73 74 @(negedge clk) 75 clr=1; 76 ld=0; 77 init=0; 78 #(CYCLE/8); 79 80 81 clr=0; 82 ld=0; 83 init=0; 84 #(10*CYCLE); 85 //clr_testbench 86 @(negedge clk); 87 clr=0; 88 ld=1; 89 init=5; 90 #(CYCLE); 91 92 clr=0; 93 ld=0; 94 init=0; 95 #(2*CYCLE); 96 97 @(negedge clk); 98 clr=0; 99 ld=1;100 init=5;101 #(2*CYCLE);102 103 clr=0;104 ld=0;105 init=0;106 #(2*CYCLE);107 108 @(negedge clk);109 clr=0;110 ld=1;111 init=5;112 #(CYCLE/8);113 114 clr=0;115 ld=0;116 init=0;117 #(10*CYCLE);118 //function testbench119 @(negedge clk);120 clr=0;121 ld=1;122 init=0;123 #(CYCLE);124 125 clr=0;126 ld=0;127 init=0;128 #(2*CYCLE);129 130 @(negedge clk);131 clr=0;132 ld=1;133 init=15;134 #(CYCLE);135 136 clr=0;137 ld=0;138 init=0;139 #(2*CYCLE);140 141 @(negedge clk);142 clr=1;143 ld=1;144 init=5;145 #(CYCLE);146 147 clr=0;148 ld=0;149 init=0;150 #(2*CYCLE);151 152 153 154 155 156 157 158 159 160 161 162 163 $finish;164 165 166 end167 168 endmodule

波形图:

编写中一个小错误:

是#(CYCLE),不是(#CYCLE).

关键词:

-

-

-

-

【世界新要闻】四位计数器testbench的设计

世界滚动:chatgpt 集成飞书实践指南

自以为是 与 思考

天天通讯!伊朗外长:伊沙恢复外交关系将为两国和地区发展注入巨大动能

世界快讯:日系车掀起买一送一热潮:买皓影插混送飞度、买日产楼兰送轩逸

天天热资讯!50万以内最舒适二排 理想L7正式交付:31.98万起售

环球新资讯:10年分红1000多亿!董明珠鼓励员工“砸锅卖铁”买格力股票

剪刀石头布的算法

资讯推荐:全球最强!传音发布260W有线、110无线快充:8分钟充满

世界观热点:美国科学家改变人类科技、终极能源即将实现?真相来了!

世界快讯:《原子之心》更新:添加FOV设置、删除种族主义动画

Shell命令-常用操作2

【质因数分解算法详解】C/Java/Go/Python/JS/Dart/Swift/Rust等不同语言实现

今亮点!霸道女总裁加盟《碟中谍8》

天天播报:00后男生每天下班后卖烤肠解压 50元投资日赚200元:厌恶刷视频、打游戏

【时快讯】网络安全(中职组)-B模块:Web安全渗透测试

环球新消息丨K8S 性能优化-K8S Node 参数调优

环球微速讯:比进口价格便宜!海南三亚榴莲今年6月将大规模上市

当废物挺好?委员称年轻人想躺平更多是调侃 奋斗的是大多数

天天亮点!中国足彩网竞彩11日推荐:曼城取胜无悬念

焦点短讯!使用SSM+Shiro+Layui框架,基于RBAC3模型开发的权限管理系统

snort入侵检测基础概述

当前播报:amusements

环球热议:6月上映!《变形金刚7》角色海报发布:擎天柱、猩猩队长亮相

【速看料】降价潮席卷全国 车企尽数参战是为何?乘联会解答:国六B要来了

观热点:01-C语言概述

环球今热点:真正油电同价!比亚迪投放“深水炸弹”:13.4万买宋Pro DM-i超级混动

环球通讯!立春来首场寒潮横扫我国大部:多地将遭遇滑梯式降温 最高降20℃

【新要闻】活久见!女生家中发现神奇圆柱形手机:登QQ、手电筒、拍照 功能多到炸

读Java性能权威指南(第2版)笔记13_堆内存下

最便宜竖折叠继任者!摩托罗拉Razr 2023真机图出炉:首次拼色后壳

当前快报:汽车价格战新进展:南北大众同日入局 丰田买一辆送一辆

世界速递!day05-功能实现04

Vue————Vue v2.7.14 入口文件【二】

【时快讯】《满江红》中国影史票房榜第6:力压《唐人街探案3》 票房突破45.23亿

环球即时:2023开门红!长四丙成功发射“一箭双星”

环球消息!第一批PCIe 5.0 SSD都是残血!14GB/s满血版还早呢

世界快资讯丨有了ChatGPT 动动嘴就能使唤Excel:我的童年梦想实现了

每日热门:8岁男孩单手打破汉诺塔世界纪录:4.305秒搞定4层

当前头条:海绵宝宝卡通图片线条图_海绵宝宝卡通图片

天生要完美电视剧28集完整版_天生要完美电视剧

对C++做爬虫的代码进行简单分析

世界热推荐:2.HelloSpring

孙海洋夫妇餐饮公司被列经营异常:本人回应

今日报丨香港男子深圳上班每天通勤4小时:月薪3万 每天通勤费用80元

【全球独家】63.C++类型转换

世界今亮点!python可变长参数

当前观察:大获成功!《最后生还者》成史上收视率最高的游戏改编剧

爆款椰子鞋停售后:阿迪在中国凉凉了

1.3kg下颜值、性能、屏幕全给你!华硕灵耀14 2023评测:续航惊人

观热点:长城汽车发布Hi4全新新能源技术:4驱享受 2驱能耗

全球关注:杠上比亚迪秦PLUS DM-i 新款日产轩逸上市:9.98万起

8GB、16GB显存的性能差多少?实测多达172%!

明解数据库------数据库存储演变史

AMD最强核显跑分上来了!但是还打不过GTX 1650 Ti

全球最新:买丰田bZ4X电动车 送一辆威驰轿车?4S店回应:活动属实

RTX 30公版显卡突然集体消失!刚刚降价40%

微头条丨公司规定不接董事长电话1次罚10000元 员工:试岗1天就走了

【全球快播报】校友承诺捐赠1100万元却不兑现被告 学校:他具备履约能力

紧跟微信步伐:支付宝掌纹支付设备外观专利获授权

【天天快播报】搅局中端市场!一加Ace2V评测:将16G满血内存进行到底

通讯!破壁机虚标功率后 疯狂小杨哥带货又翻车:面霜因虚假宣传被罚

《王者荣耀》出海“首战告捷”:登顶巴西免费游戏榜

环球报道:记录--vue3+setup+ts 知识总结

【世界速看料】程序员养发神器:拒绝加班熬夜,告别秃头!

【世界聚看点】【希尔排序ShellSort算法详解】Java/Go/Python/JS/C不同语言实现

环球微头条丨【分享贴】项目中为啥总是项目经理一人干着急?

使用PostgreSQL而不是MySQL存储中型数据有什么好处?

3000块多品牌SSD质量大PK:整体比机械硬盘可靠

玩家购入二手Switch主机:可是被卖家坑惨了

航班晚点1小时 机长提速提前20分钟到达帮助乘客换机?山航回应

每人1600元!北京发放首批“京彩·绿色”消费券:买手机PC都能用

当前热文:涉及121万辆!我国2022年新能源汽车召回量创历史新高:电池、电机缺陷多

环球最资讯丨暴风的恋人百度云_暴风的恋人

有监督学习——线性回归

禁用XXE处理漫谈

腾讯-广点通转化归因

来真的!贾跃亭:3月30日生产FF91 百万豪车来了

【天天新视野】30个汽车品牌降价 成都发放消费券:满40万可减8000元

【世界独家】华硕发布TUF Gaming M3 Gen II鼠标:仅重59g、IP56防尘防水

全球今亮点!过期1天的食物还能吃吗?

日系中的另类!国产马自达CX-50内饰发布:原汁原味引入海外版

加速资源整合,星纪魅族围绕手机、XR、前瞻技术拓展智能生态

Prompt-Engineering-Guide 学习摘要2

今日关注:电动汽车综合检测

观焦点:这几个群,程序员可千万不要进!

每日快讯!12万元买宝马“3系”?宝马中国回应降价传闻:指导价没变

当前快讯:玩家不满《魔戒:咕噜》新宣传片:他没有主角光环!

环球热讯:小米搞出“新花样”:可层叠摄像模组专利获授权

焦点快报!没有秘密了!AI或能够读取大脑重现梦境

今日快看!新老代表接力提建议将牡丹定为国花:100多个国家都有国花了

【天天报资讯】山西李家大院哪些人可以享受半价票优惠

环球新资讯:【机器学习】1. 广义线性模型

【世界新视野】密码学报如何正确Latex投稿?

环球今亮点!快 40 岁,刚被裁。。

金三银四每天一个.NET基础知识巩固(一)

今日要闻!从“13 天”到“0 天”延时,揭秘火山引擎 DataLeap SLA 保障最佳实践

世界热消息:谷歌报复性砸出5620亿参数大模型:比ChatGPT更恐怖 学术圈已刷屏

【环球播资讯】2月国产游戏出海成绩出炉:《原神》获收入和增长双料冠军

Nginx http 文件服务器 中文名称文件乱码以及不能访问下载问题 (解决全过程)