最新要闻

- 环球观热点:不含SMR好评 希捷22TB NAS专用硬盘开卖:只要4200多

- 酷派大观50s现身电信产品库:天玑700 720P分辨率

- 全球观察:新能源车越卖越亏?广汽董事长曾庆洪:钱让外国朋友赚了

- 时隔22年 微软发布WinXP蓝天白云壁纸4K高清版:免费下载

- iQOO杀疯了!1TB UFS 4.0闪存只要3699元:同档位绝无仅有 环球视点

- 迪士尼被曝大量低价团购票无法入园 平台回应:旅行社操作失误 全球信息

- 5.8英寸塞进骁龙8 Gne2!小屏旗舰华硕Zenfone 10海外官宣

- 余承东同款座驾!AITO问界M5智驾版下周开启交付

- 保时捷发布史上最有科技感纯电超跑Mission X:动力超过1000匹 极速320公里/小时_消息

- 马斯克嘲讽苹果AR头显:花3500美元买它 不如20美元买包致幻菇_全球看热讯

- 天天讯息:浓烟下的美国:N95口罩销量猛增逾10倍、中国产空气净化器大卖

- 环球时讯:16GB/32GB内存笔记本对比实测:16GB不够用了

- 讯飞星火认知大模型V1.5正式发布:知识问答突破 可以告别搜索了-环球百事通

- 2023年底更多极端天气来袭 美国警告厄尔尼诺已形成-世界热门

- 快资讯:特朗普因机密文件案被起诉 将于下星期出庭

- 快舟一号甲固体火箭第20次发射:“导里导气”

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

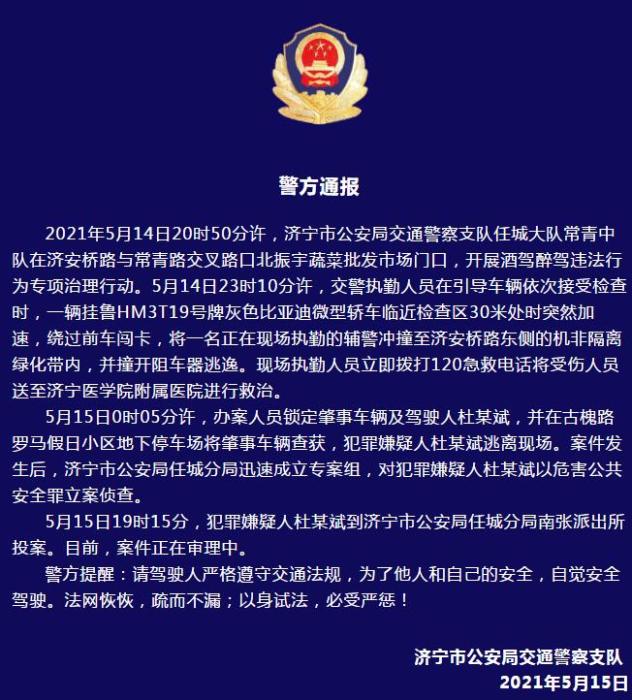

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

18-状态机_环球滚动

1.状态机

FPGA是并行执行的,如果想要处理具有前后顺序的事件就要使用状态机

1.1 状态机是什么?

- 状态机简写为 FSM(Finite State Machine),也称为同步有限状态机,我们一般简称为状态机,之所以说“同步”是因为状态机中所有的状态跳转都是在时钟的作用下进行的,而“有限”则是说状态的个数是有限的。

- 状态机根据影响输出的原因分为两种:Moore型或者是Mealy型

- 两种状态机的共同点:状态的跳转都只和输入有关。区别主要是在输出的时候:若最后的输出只和当前状态有关而与输入无关则称为 Moore 型状态机;****若最后的输出不仅和当前状态有关还和输入有关则称为 Mealy 型状态机。

- 状态机是时序逻辑电路中非常重要的一个应用,常在大型复杂的系统中使用较多。

状态机的每一个状态代表一个事件,从执行当前事件到执行另一事件我们称之为状态的跳转或状态的转移,我们需要做的就是执行该事件然后跳转到一下时间,这样我们的系统就“活”了,状态机特别适合描述那些发生有先后顺序或时序规律的事情,在数字电路系统中小到计数器大到微处理器都可以用状态机来进行描述。其实状态机也是一种函数关系,如上图所示,一个计数器其实就可以看作是一个最简单的状态机,输入是时钟信号,状态是计数的值,输出是计数的值,我们可以列出一个时间和输出的函数关系,函数表达式为 q = counter(t),坐标关系如图所示,在有限的时间内,我们都可以根据具体的时间来算出当前输出的值是多少。

2. 可乐售卖机案例

可乐机每次只能投入 1 枚 1 元硬币,且每瓶可乐卖 3 元钱,即投入 3 个硬币就可以让可乐机出可乐,如果投币不够 3 元想放弃投币需要按复位键,否则之前投入的钱不能退回。

(资料图片仅供参考)

(资料图片仅供参考)

2.1 状态机框图

- 必不可少的是时钟和复位信号;其次是投币 1 元的输入信号,我们取名为 pi_money;可乐机输出我们购买的可乐,取名为 po_cola。

- 只能投入1元的硬币,没有找零

2.2 状态转移图

- 每个椭圆的框表示一个状态(也可以用其他图形表示)

- 每个状态之间都有一个指向的箭头,表示的是状态跳转的过程

- 箭头上有标注的一组数字,斜杠左边表达的是状态的输入,斜杠右边表达的是状态的输出

完整的状态转移图需要知道以下三个要素:1、输入:根据输入可以确定是否需要进行状态跳转以及输出,是影响状态机系统执行过程的重要驱动力;2、输出:根据当前时刻的状态以及输入,是状态机系统最终要执行的动作;3、状态:根据输入和上一状态决定当前时刻所处的状态,是状态机系统执行的一个稳定的过程。

2.3 可乐机状态转移图

1、输入:投入 1 元硬币;2、输出:出可乐、不出可乐;3、状态:可乐机中有 0 元、可乐机中有 1 元、可乐机中有 2 元、可乐机中有 3 元。

- 从IDLE状态开始进行分析,IDLE状态有两种情况,投入硬币或者不投入硬币,不投入硬币维持IDLE状态,投入硬币跳转到下一个状态,依次进行分析

- 这是Moore型的状态机,输入只与当前的状态有关,与输入没有关系

- 如果不写THREE状态,在TWO状态的时候投入一元,此时出可乐,并且状态变为IDLE,如果此时不投钱,维持TWO状态 - 这种就是Mealy型状态机

2.4 波形图

状态转移图画出了之后可以不用画波形图

- 首先是三个输入信号,我们随机模拟输入信号 pi_money 的输入情况,根据状态转移图来分析继续绘制波形。

- 因为有不同的状态之间的跳转关系,所以我们需要一个用于表示状态的变量,一般都取一个名为 state 的状态变量,state 处于哪个状态、何时跳转都需要根据输入信号pi_money 来决定

- 而输出信号 po_cola 的结果则由输入 pi_money 和当前 state 的状态共同决定。

2.5 RTL

信号:时钟和复位信号,还有输入信号(可能有多个输入信号)、输出信号

状态参数(通过参数定义中间状态方便阅读及修改):多个状态需要定义多个状态参数

状态参数编码:多个状态可以使用独热码的编码方式或者其他的编码方式(二进制码、格雷码)

状态变量 - 使用独热码的话,有多少个中间状态,中间变量就有多少位

中间变量(计数器等)

对状态变量和中间变量进行赋值

对输出信号进行赋值

2.5.1 两段式状态机

第一段状态机写状态的跳转,第二段状态机写数据的输出

module simple_fsm(input wire sys_clk,input wire sys_rst_n,input wire pi_money,output reg po_cola);parameter IDLE = 3"b001; ONE = 3"b010; TWO = 3"b100;reg [2:0] state;// 第一段状态机描述当前状态如何跳转到下一个状态always @ (posedge sys_clk or negedge sys_rst_n)if(sys_rst_n == 1"b0)state <= IDLE;else case(state)IDLE : if(pi_money == 1"b1)state <= ONE;else state <= IDLE;ONE : if(pi_money == 1"b1)state <= TWO;else state <= ONE;TWO : if(pi_money == 1"b1)state <= IDLE;else state <= TWO;default :state <= IDLE;endcase//第二段状态机,描述当前状态 state 和输入 pi_money 如何影响 po_cola 输出always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n == 1"b0)po_cola <= 1"b0;else if((state == TWO) && (pi_money == 1"b1))po_cola <= 1"b1;elsepo_cola <= 1"b0;endmodule- 端口列表部分

- 状态编码部分

- 状态变量

- 第一段状态机部分

- 第二段状态机部分

2.5.2 三段式状态机

module simple_fsm(input wire sys_clk,input wire sys_rst_n,input wire pi_money,output reg po_cola);parameter IDLE = 3"b001; ONE = 3"b010; TWO = 3"b100;reg [2:0] cur_state;reg [2:0] next_state;// 第一段状态机描述当前状态always @(posedge sys_clk or sys_rst_n)if(sys_rst_n == 1"b0)cur_state <= IDLE;else cur_state <= next_state;// 第二段描述如何跳转到下一个状态always @ (*)case(state) IDLE : if(pi_money == 1"b1)state <= ONE;else state <= IDLE;ONE : if(pi_money == 1"b1)state <= TWO;else state <= ONE;TWO : if(pi_money == 1"b1)state <= IDLE;else state <= TWO;default :state <= IDLE;endcase//第三段状态机,描述当前状态 state 和输入 pi_money 如何影响 po_cola 输出always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n == 1"b0)po_cola <= 1"b0;else if((state == TWO) && (pi_money == 1"b1))po_cola <= 1"b1;elsepo_cola <= 1"b0;// 第三段assign po_cola = state == TWO && pi_money == 1"b1 ? 1"b1 : 1"b0;endmodule2.6 状态机分段

状态机代码写法有一段式、二段式、三段式

- 一段式指的是在一段状态机中使用时序逻辑既描述状态的转移,也描述数据的输出

- 二段式指在第一段状态机中使用时序逻辑描述状态转移,在第二段状态机中使用组合逻辑描述数据的输出

- 三段式指在第一段状态机中采用时序逻辑描述状态转移,在第二段在状态机中采用组合逻辑判断状态转移条件描述状态转移规律,在第三段状态机中描述状态输出,可以用组合电路输出,也可以时序电路输出)。这种一段式、二段式、三段式其实都是之前经典的老写法,也是一些老工程师仍然习惯用的写法,老方法是根据状态机理论建立的模型抽象后设计的,其实要严格按照固定的格式来写代码,否则综合器将无法识别出你写的代码是个状态机,因为早期的开发工具只能识别出固定的状态机格式,如果不按照标准格式写代码综合器最后无法综合成为状态机的样子。这样往往增加了设计的难度,很多人学习的时候还要去了解理论模型,反复学习理解很久才能够设计好的状态机,所以需要我们改进。老的一段式、二段式、三段式各有优缺点

- 一段式在描述大型状态机时会比较困难,会使整个系统显得十分臃肿,不够清晰

- 二段式状态机的好处是其结构和理想的理论模型完全吻合,即不会有附加的结构存在,比较精简,但是由于二段状态机的第二段是组合逻辑描述数据的输出,所以有一些情况是无法描述的,比如输出时需要类似计数的累加情况,这种情况在组合逻辑中会产生自迭代,自迭代在组合逻辑电路中是严格禁止的,而且第二段状态机主要是描述数据的输出,输出时使用组合逻辑往往会产生更多的毛刺,所以并不推荐。

- 三段式状态机,三段状态机的输出就可是时序逻辑了,但是其结构并不是最精简的了。三段式状态机的第一段状态机是用时序逻辑描述当前状态,第二段状态机是用组合逻辑描述下一状态,如果把这两个部分进行合并而第三段状态机保持不变,就是我们现在最新的二段式状态机了。这种新的写法在现在不同综合器中都可以被识别出来,这样既消除了组合逻辑可能产生的毛刺,又减小了代码量,还更加容易上手,不必再去关心理论模型是怎样的,仅仅根据状态转移图就非常容易实现,对初学者来说十分友好。所以我们习惯性的使用两个均采用时序逻辑的 always 块,第一个 always 块描述状态的转移为第一段状态机,第二个 always 块描述数据的输出为第二段状态机(如果我们遵循一个 always 块只描述一个变量的原则,如果有多个输出时第二段状态机就可以分为多个always 块来表达,但理论上仍属于新二段状态机,所以几段式状态机并不是由 always 块的数量简单决定的)。

2.7 Testbench

`timescale 1ns/1nsmodule tb_simple_fsm();//reg definereg sys_clk ;reg sys_rst_n ;reg pi_money ; //wire definewire po_cola; //初始化系统时钟、全局复位initial beginsys_clk = 1"b1;sys_rst_n <= 1"b0;#20sys_rst_n <= 1"b1;end //sys_clk:模拟系统时钟,每 10ns 电平翻转一次,周期为 20ns,频率为 50MHzalways #10 sys_clk = ~sys_clk; //pi_money:产生输入随机数,模拟投币 1 元的情况always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n == 1"b0)pi_money <= 1"b0;elsepi_money <= {$random} % 2; //取模求余数,产生非负随机数 0、1 //将 RTL 模块中的内部信号引入到 Testbench 模块中进行观察,使用wire类型变量wire [2:0] state = simple_fsm_inst.state; initial begin$timeformat(-9, 0, "ns", 6);$monitor("@time %t: pi_money=%b state=%b po_cola=%b", $time, pi_money, state, po_cola);end //------------------------simple_fsm_inst------------------------simple_fsm simple_fsm_inst(.sys_clk (sys_clk ), //input sys_clk.sys_rst_n (sys_rst_n ), //input sys_rst_n.pi_money (pi_money ), //input pi_money .po_cola (po_cola ) //output po_cola); endmodule关键词:

-

-

-

天天热讯:生态 | Eolink x 火线安全,构建高效安全的一体化研测管理体系

18-状态机_环球滚动

CCSP2019T2_纸牌计数 | 2019苏州CCSP大学生计算机系统与程序设计竞赛

天天热讯:生态 | Eolink x 火线安全,构建高效安全的一体化研测管理体系

Java 集合框架体系简介

【财经分析】绿色低碳转型亟需新动力 中国转型类债券市场蓄势待发 天天新资讯

环球观热点:不含SMR好评 希捷22TB NAS专用硬盘开卖:只要4200多

酷派大观50s现身电信产品库:天玑700 720P分辨率

全球观察:新能源车越卖越亏?广汽董事长曾庆洪:钱让外国朋友赚了

时隔22年 微软发布WinXP蓝天白云壁纸4K高清版:免费下载

浅谈这些年如何被MDK, IAR, GCC和厂家SDK版本兼容性“蹂躏”, 一代版本一代坑|世界头条

热点聚焦:java-基础安装-基础

环球视讯!数据的图像化之旅:探索GIS与可视化的无限可能

【独家】百度人脸识别_SpringBoot整合离线SDK

天天热讯:UDS统一诊断服务

【新华500】新华500指数(989001)9日涨0.45%

iQOO杀疯了!1TB UFS 4.0闪存只要3699元:同档位绝无仅有 环球视点

迪士尼被曝大量低价团购票无法入园 平台回应:旅行社操作失误 全球信息

5.8英寸塞进骁龙8 Gne2!小屏旗舰华硕Zenfone 10海外官宣

余承东同款座驾!AITO问界M5智驾版下周开启交付

保时捷发布史上最有科技感纯电超跑Mission X:动力超过1000匹 极速320公里/小时_消息

今日关注:17-呼吸灯

华为云 UCS GitOps:轻松交付多集群云原生应用

全球速看:OPEN AI 全新版本来了2.0.0永久免费在线体验构建AI开放生态

Angular4 教程_编程入门自学教程_菜鸟教程-免费教程分享

虚拟列表

马斯克嘲讽苹果AR头显:花3500美元买它 不如20美元买包致幻菇_全球看热讯

天天讯息:浓烟下的美国:N95口罩销量猛增逾10倍、中国产空气净化器大卖

环球时讯:16GB/32GB内存笔记本对比实测:16GB不够用了

讯飞星火认知大模型V1.5正式发布:知识问答突破 可以告别搜索了-环球百事通

2023年底更多极端天气来袭 美国警告厄尔尼诺已形成-世界热门

快资讯:特朗普因机密文件案被起诉 将于下星期出庭

车载雷达报警测试要点

快舟一号甲固体火箭第20次发射:“导里导气”

英国政府将对油气公司征收暴利税设定门槛

天天热点!.NET的8种JSON序列化反序列化工具供你选择

端午节火车票开售 热门车票“秒空”

基建狂魔新作!世界上建设难度最高的跨海集群工程:深中通道

另外赠送洁面乳:多芬氨基酸洁面泡泡2瓶49.9元发车(新低)|每日报道

全球短讯!大叔被疑偷拍自证清白后仍遭女子曝光 网友:太欺负人

考生考前与老师闲聊押中英语作文:十分幸运

陕西一考生考前与老师闲聊押中英语作文:十分幸运,考完第一时间找老师表达喜悦

茶颜悦色杯底现镊子,工作人员:是夹茶叶用的,已处理中|今日视点

住房公积金制度惠及面进一步扩大 去年全国发放贷款超万亿元|天天实时

天天关注:WPF中有中心点的slider滑动条

世界头条:易基因:全基因组DNA甲基化和小RNA分析揭示甘蓝型油菜种子的基因组不对称性

接口防刷处理方案,太优雅了!

Linux磁盘分区扩容-世界今亮点

ChatGTP:没人比我更懂诗歌_当前头条

四部门:深入开展家电以旧换新_天天即时看

美国铀期货U3O8价格于6月7日涨至56.25美元

方便英文单词_方便英文

医疗产业ETF(159877)涨0.67%,开立医疗涨5.08%,华兰股份涨5.31%

全球看点:唯美的歌词带意境(唯美的歌词)

天天快讯:中国无人驾驶高速地铁海外开工:最大载客量达1100人

16核i9+RTX 4060游戏本价格也被国产打下来了 七彩虹将星X15仅售5999|每日聚焦

【新要闻】赛力斯董事长张兴海:恶性竞争将毁掉企业和行业

全球关注:低头玩手机等于颈椎增压45斤!相当于6岁小孩骑脖子

马斯克要横扫欧洲!特斯拉全新超级工厂曝光:投资超300亿 或落地西班牙

陆家嘴数智天地·智慧谷项目亮相 金融科技企业拟在此设立研发总部

天天滚动:双方家长有矛盾怎么办 双方家长有矛盾怎么解决

全球微资讯!websocket

海外直播源码技术文字聊天功能的配置_当前速讯

深入浅出Spring原理及实战「缓存Cache开发系列」

每日快看:缯怎么读怎么组词_缯怎么读

环球时讯:英特尔开始停产11代处理器

王治郅视频_王治郅事件-全球最新

莫兰迪作品高清大图_莫兰迪作品 每日精选

天天消息!22.5万起 小鹏G6开启预售 官方:真正的6边形战士来了

全球实时:惠普推出新款无线耳机:充电盒自带触控屏 控制音乐播放

全球快播:高考考生遇采访喊话:取消调休 取消调休

网购格力空调收到“木各力”牌 商家拒绝退款

余承东:特斯拉FSD进入中国我们也不怕 依然可以遥遥领先

焦点快播:gtx260m显卡(gtx260m)

高考前最后一课丨常德市七中老师收到全班学生送的礼物 笑着笑着就哭了_当前快讯

dnf带幻影的史诗武器(dnf幻影手镯) 世界热闻

当前速递!猪菜磨底VS服务回暖!5月CPI或小幅反弹

热讯:流年

世界百事通!深度学习应用篇-计算机视觉-语义分割综述[5]:FCN、SegNet、Deeplab等分割算法、常用二维三维半立体数据集汇总、前景展望等

每日资讯:美团太细了:Springcloud 微服务优雅停机,如何实现?

全网Jenkins+Gitee+Docker/SSH 部署避坑点总结 每日关注

全球通讯!人工智能(AI)热潮提振了的科技股,并推高了对冲基金的回报,帮助他们挽回去年的损失

今日快讯:热力学第一定律功能关系(热力学第一定律)

热消息:favorite subject(favorite)

天天看点:辽宁省沈阳市2023-06-06 16:27发布大风蓝色预警

每日报道:qq显示iphone在线没有显示4g(qq显示iphone在线)

全球百事通!正整数包括什么分数(正整数包括什么)

鸡汤用高压锅煮要煮多久 高压锅炖鸡汤要压多少分钟

守护者之铠(永恒守护者腿铠)-全球消息

充满“海洋”味!比亚迪宋PLUS冠军版来了:选它还是四驱哈弗枭龙MAX

世界热头条丨精装版丰田陆巡 全新雷克萨斯GX全球首发:能越野的日系豪华!

美国一列满载全新汽车的火车脱轨:弯弯曲曲扭成“贪吃蛇”

快消息!K60系列终极大作!曝Redmi K60 Ultra 7月登场

重庆一女生考完哭着说终于不用做数学了:网友神回复-焦点观察

汉字的演变历史手抄报_汉字的演变历史 天天最新

高考“钉子户”梁实谈第27次高考:文综重大失误

世界短讯!珍惜时间的名人小故事(珍惜时间的名人)

全球播报:百度贴吧怎么注册帐号登录(百度贴吧怎么注册帐号)

热推荐:太极杨氏85赵斌视频(赵斌杨氏85式太极拳)

Nginx安装部署及性能优化 当前看点

每日动态!Map