最新要闻

- 浙商入川觅商机:签约项目34个 投资金额达138亿元|世界关注

- 可追溯至40年前!日立本田合资零件厂承认长期造假

- 环球新资讯:必应取代百度成中国第一?百度:数据离谱 中文搜索有自信第一

- 每日报道:租客仅剩13元花11元买瓜探望房东:情义无价!满满正能量

- 爱奇艺辟谣子公司将裁员50%:不实 法务部门已介入

- 圣农发展:4月份销量降低是源于公司预判后期市场持续向好,增加了部分的战略库存 环球时快讯

- 宁波美诺华天康药业有限公司获得盐酸莫西沙星片药品注册批件

- 要闻速递:长城举报比亚迪排放不达标 检测机构中汽研:集团后续统一回复

- 《蜘蛛侠:纵横宇宙》大闹天宫海报公布:6月2日上映

- 美国交通部长:对特斯拉L2级智能驾驶感到担忧

- 5G网速起飞!小米13 Ultra双卡上网来了:下载速度猛增30% 天天最新

- 宝骏悦也上市 五菱大船转身:人民想要什么就造什么

- 天天信息:福建省第二届短视频大赛正式启动

- 5月31日发布会!法拉第未来5月底启动FF 91第一阶段交付

- 男子弄丢价值百万唐伯虎真迹:好心市民捡到后交还 快资讯

- 618来了!AMD Zen4价格跳水:锐龙9 7950X上市半年直接6折|天天快资讯

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

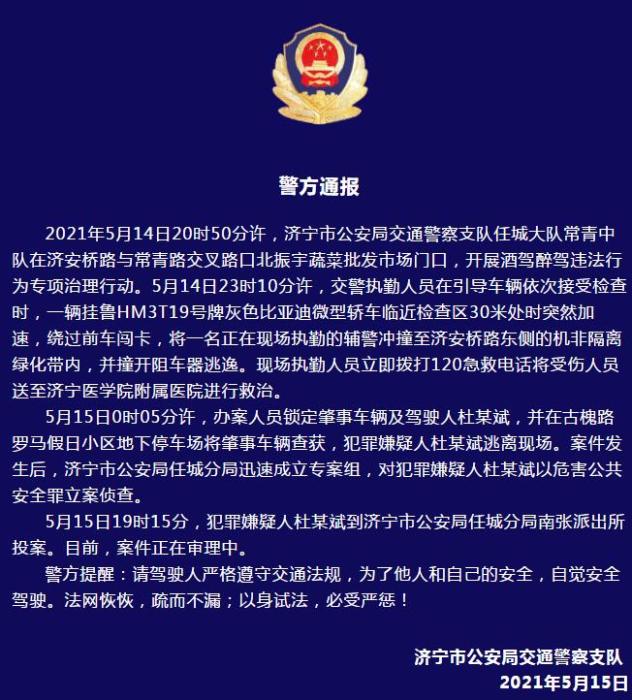

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

11-计数器

(相关资料图)

(相关资料图)

1.计数器

FPGA中一切与时间有关的电路都会使用到计数器计数是一种最简单的基本运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量\计数和控制的功能,同时兼有分频功能.计数器在数字系统中应用广泛,如电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中做乘法,除法运算时记下加法\减法次数;有如在数字仪器中对脉冲的计数等计数器在FPGA最常用的时序逻辑电路,通过计数器可以知道各个信号之间的关系计数器一般从0开始计数,计满清0或者是计到一定次数清0

2. FPGA实现

- 前0.5s处于点亮状态,后0.5s处于熄灭状态

2.1 计数器设计关键

计数器关键:什么时候开始计数,什么时候清零

- 计数器在复位信号撤销之后,时钟沿到来就可以立即进行计数

- 计数器清0:计满或者计到需要的值,哪一个值是需要计到的值?比如需要计数1s,就需要知道计数器计多少个数(50M时钟)

- f = 50MHz = 50000KHz = 50000_000(十进制)Hz,单位时间内信号进行周期性变化的次数,50000_000Hz表示单位时间内进行了50000_000次周期性变化,每次变化所用的时间为t

- t = 1/f = (1/50000_000) = 20ns -- 时钟周期,计数器每一次计数经过的时间为20ns

- 计数器需要计数的个数M:M = 1s/20ns = 5*10^7

- 计数器的最大值是:M-1(从0开始计数)

2.2 模块框图和波形图

- 计数器是对时钟信号进行计数,所以要有时钟信号,复位信号

- 引出一路输出信号到LED灯波形图绘制非常重要,按照时钟,复位信号,输入,输出的顺序画波形图

- 设置一个中间变量进行计数,复位信号下赋予初值,复位信号撤销且在上升沿开始计数优化

- 计数到M/2-1之后进行清零,再计数到M/2-1之后再次清0,也可以实现上述前0.5s灯亮,后0.5s灯灭,且每次计数都是M/2

- 第一种条件下计数到M-1(4999999),转化为二进制需要26bit,优化之后计数到M/2-1(2499999)需要使用25bit,节省资源量

2.3 RTL

module counter#( parameter CNT_MAX = 25"d24_999_999 // 例化模块的参数传递接口,参数之间加,)( input wire sys_clk, input wire sys_rst_n, output reg led_out); // 声明计数器变量,位宽25bit reg [24:0] cnt; // 参数定义 // 计数器的计数最大值 // parameter可以用与模块内部,也可以用于参数例化模块的参数传递 parameter CNT_MAX = 25"d24_999_999; // 普通模块参数定义 // localparam CNT_MAX = 25"d24_999_999; // 只用于模块内部 counter #( .CNT_MAX (100); // 实例化的时候参数也写在这个位置,并且可以修改参数 ) counter_inst1 // 带有参数的模块实例化的模块名称写在参数列表之后 ( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .led_out (led_out) ); counter #( .CNT_MAX (100); // 实例化的时候参数也写在这个位置,并且可以修改参数 ) // 多个模块实例化可以传递不同的参数 counter_inst1 ( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .led_out (led_out) );endmodulemodule counter#( parameter CNT_MAX = 25"d24_999_999; // 例化模块的参数传递接口)( input wire sys_clk, input wire sys_rst_n, output reg led_out); // 声明计数器变量,位宽25bit reg [24:0] cnt; // 计数器变量赋值 always @ (posedge sys_clk or negedge sys_rst_n) begin if(sys_rst_n == 1"b0) begin cnt <= 25"d0; end else if(cnt = CNT_MAX) begin cnt <= 25"b0; end else cnt <= cnt + 25"d1; end // 输出信号赋值 always@(posedge sys_clk pr negedge sys_clk_n) begin if(sys_rst_n == 1"b0) led_out <= 1"b0; else if(cnt == CNT_MAX) led_out <= ~led_out; else led_out <= led_out; endendmodule- 编译代码

2.4 Testbench

`timescale 1ns/1nsmodule tb_counter(); reg sys_clk; reg sys_rst_n; wire led_out; initial begin sys_clk = 1"b1; sys_rst_n <= 1"b0; #20; sys_rst_n <= 1"b1; end always #10 sys_clk = ~sys_clk; counter #( .CNT_MAX (25"d24) ) counter_inst ( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .led_out (led_out) );endmodule2.5 上板验证

2.6 其他方式实现

- 当计数器计满之后,添加一个cnt_reg变量,给这个变量的信号产生一个周期的脉冲(拉高一个周期),然后拉低

- cnt信号正常

- led_out信号在检测到cnt_flag信号为高电平的时候,会进行一次翻转

- 使用脉冲标志信号cnt_flag,当计数器计数到M/2-2的时候,在下一个周期(M/2-1)周期上升沿产生一个脉冲,同样在cnt_flag信号拉高的时候led_out进行翻转,这样就能实现led_out和计数信号同步,没有延迟周期引入脉冲标志信号cnt_flag,可以简化if中的条件语句,在进行复杂设计的时候可以节省资源

module counter#( parameter CNT_MAX = 25"d24_999_999; // 例化模块的参数传递接口)( input wire sys_clk, input wire sys_rst_n, output reg led_out); // 声明计数器变量,位宽25bit reg [24:0] cnt; reg cnt_flag; // 计数器变量赋值 always @ (posedge sys_clk or negedge sys_rst_n) begin if(sys_rst_n == 1"b0) begin cnt <= 25"d0; end else if(cnt = CNT_MAX) begin cnt <= 25"b0; end else cnt <= cnt + 25"d1; end // 计数器标志位赋值 always @ (posedge sys_clk or negedge sys_rst_n) if(sys_rst_n == 1"b0) cnt_flag <= 1"b0; else if(cnt ==(CNT_MAX - 25"d1)) cnt_flag <= 1"b1; else cnt_flag <= 1"b0; // 输出信号赋值 always@(posedge sys_clk pr negedge sys_clk_n) begin if(sys_rst_n == 1"b0) led_out <= 1"b0; else if(cnt_flag == 1"b1) led_out <= ~led_out; else led_out <= led_out; endendmodule关键词:

-

-

-

-

11-计数器

最新消息:位运算在排序算法中的运用

浙商入川觅商机:签约项目34个 投资金额达138亿元|世界关注

惠誉发出评级警告 美债僵局如何收场|全球热议

【全球报资讯】惠誉发出评级警告 美债僵局如何收场

可追溯至40年前!日立本田合资零件厂承认长期造假

环球新资讯:必应取代百度成中国第一?百度:数据离谱 中文搜索有自信第一

每日报道:租客仅剩13元花11元买瓜探望房东:情义无价!满满正能量

爱奇艺辟谣子公司将裁员50%:不实 法务部门已介入

圣农发展:4月份销量降低是源于公司预判后期市场持续向好,增加了部分的战略库存 环球时快讯

宁波美诺华天康药业有限公司获得盐酸莫西沙星片药品注册批件

关于linux系统中umask值的说明-以及计算转换成默认权限符号的方法

焦点热议:记录--超长溢出头部省略打点,坑这么大,技巧这么多?

环球即时看!跟着hsp学springmvc--数字格式化介绍

5)基本查询语句|焦点快看

要闻速递:长城举报比亚迪排放不达标 检测机构中汽研:集团后续统一回复

《蜘蛛侠:纵横宇宙》大闹天宫海报公布:6月2日上映

美国交通部长:对特斯拉L2级智能驾驶感到担忧

5G网速起飞!小米13 Ultra双卡上网来了:下载速度猛增30% 天天最新

宝骏悦也上市 五菱大船转身:人民想要什么就造什么

世界看点:[IDEA]社区版IDEA的数据库连接插件(DB Navigator)

项目终于用上了 Spring 状态机,非常优雅!

全球热推荐:编译静态库遇到的 LNK2019 报错

通讯!Swift中常见的String用法,Array高阶使用,Set集合操作

天天信息:福建省第二届短视频大赛正式启动

5月31日发布会!法拉第未来5月底启动FF 91第一阶段交付

男子弄丢价值百万唐伯虎真迹:好心市民捡到后交还 快资讯

618来了!AMD Zen4价格跳水:锐龙9 7950X上市半年直接6折|天天快资讯

世界即时看!“熊孩子”惹祸:女童剪掉顾客一撮头发 家长赔1万多

到底谁会买?《魔戒:咕噜》口碑扑街:媒体均分低至38分

【环球聚看点】Oracle迁移到MySQL时数据类型转换问题

SpringBoot结合easyexcel处理Excel文件-全球焦点

【打怪升级】【容器】关于Map

全球微动态丨海康威视SDK - 非非门禁和报警主机产品的用户密码设置

每日资讯:游戏逆向-D3D9绘制

59岁水均益罕现身和富婆合影,吃大餐喝名贵酒,模样大变发福油腻

债市日报:5月25日

比奥迪Q3更值得买!全新凯迪拉克GT4官图发布:颜值真能打 时讯

要涨价了!上海迪士尼6月23日起门票调价 世界动态

OpenAI CEO:在重压下会考虑退出欧洲市场

双飞燕推出VM20蓝牙鼠标:用嘴“打字”见过没

新西兰航空空乘努力用中文报菜名 拍摄者:他不懂中文但努力服务 环球快报

大阪宝可梦中心因发放特别宝可梦卡造成人潮混乱 现场一片狼藉

微信向部分Windows用户推送版本更新 现已增加锁定功能

苹果于国外上架可定位控温旅行杯 售价高达1413元引发网友吐槽

前《战地》创意总监成立新工作室 称正在研发在线射击游戏

热头条丨linux shell编程规范和变量

idea修改idea64.exe.vmoptions导致打不开问题

全球热文:突围低代码下半场,未来悬而未决

Python集合 (set) 的增删改查及 copy()方法_焦点简讯

苹果iOS 17将改进锁屏界面 会使iPhone变成家居智能屏幕

我国研究团队成功研制出高柔韧性单晶硅太阳电池 可以像纸片一样弯曲

药学基本题(药学基本知识)_天天快资讯

惠普打印机型号有哪些?惠普打印机墨盒怎么加墨水?

每日机构分析:5月25日

环球速看:双13.3寸OLED触屏!联想YOGA Book 9i国内发布:16999元

长城举报比亚迪排放不达标背后:专家称如果坐实 审核标准会被动摇|天天关注

全球仅此一份!布加迪在迪拜推出首批住宅:每家均独一无二 当前独家

30万魅友参与!魅族20新配色定名“独白”:行业唯一白面板机身|天天聚看点

中国电影华表奖颁奖典礼太接地气:一大波明星坐路边等待 环球微头条

2023年安徽合肥公积金缴存基数标准调整 3月1日起执行!

上海SIAL食品博览会成功举办!济州品牌初露头角!

它来了!真正的 python 多线程

KKRT-PSI

环球简讯:创新应用场景下的可视化大屏:重新定义信息展示

今日视点:如何证明Servlet是单例的?

构建高可用云原生应用,如何有效进行流量管理?

天天观天下!【新华500】新华500指数(989001)25日下跌0.22%

学堂有名堂|30分钟午睡时间,教室里睡不着睡不好怎么办?黄浦区这所小学展开了研究

比亚迪高管回怼长城举报:挡别人的路 不会让自己行得更远|天天消息

单价6.5亿 国产大飞机快能坐了 东航C919将于近期投入实际运营 当前要闻

全球播报:恩怨还没完!暴雪在中国起诉网易雷火公司

顶配16999元 联想YOGA Air 32 4K一体机发布:13代i9+RTX 4050 一线连所有

1.28kg超轻身材!联想发布YOGA Air 14s 2023轻盈本 天天微资讯

【PC迁移与管理】上海道宁为每个用户和每个 PC 传输和迁移场景提供解决方案——PCmover_每日热讯

天天热推荐:Pytest - setup 和 teardown

全球即时看!yolov5+deepsort+slowfast复现

全国护肤日(国际爱肤日):关注内外抗衰 远离皮肤疾病

最美小米手机!小米Civi 3亮相

减肥新方法!研究证实画饼真的能充饥|焦点滚动

新一代自拍之王!小米Civi 3前置双主摄:拍照Vlog全面兼顾 天天即时

称比亚迪污染物排放不达标 长城举报的是个啥:油箱成争议焦点

暖心!国羽苏杯夺冠黄东萍视频连线王懿律,黄鸭组合一同登台领奖

Maven的核心解压与配置 观热点

当前通讯!你怎么看?统计称上海人能挣钱更能花钱 全国北京人赚的钱最耐花

图灵奖得主:人类大脑是生物机器 一定会有超级AI超越它 今日热议

焦点消息!《雨血》精神续作!国产黑暗武侠大作《影之刃零》发布首支预告

天天关注:黄芪加枸杞大枣泡水喝的功效与作用 枸杞大枣泡水喝的功效与作用

SRE心里话:要求100%服务可用性就是老板的无知_环球信息

助数字人民币“飞入寻常百姓家”

国外玩家吐槽PS发布会拉跨:是不是最差的一届?-环球新资讯

消失70多年 一度被认为灭绝:广西发现珍稀植物巨型蜘蛛抱蛋

世界今日讯!AMD超算三连冠!唯一投入实用的百亿亿次

高性价高颜值轻薄本代表作!华硕无畏15 2023 4299元首发抢购中|世界快播

焦点速读:老人遛狗不牵绳还将猫踢飞 网友吵翻:这是在保护猫 你怎么看?

焦点资讯:5人5月用容器技术保卫蓝天

关于 Workstation Pro 的基础知识

文物 | 博物馆文物的数字化保护与管理

马上就要过期的食品打一折:能买吗?安全吗?

马斯克计划打造世界第三大AI公司 或整合特斯拉和推特