最新要闻

- 快报:我国南海发现两处古代沉船

- 我国深海考古重大进展!首次发现大型古代沉船:水下第一视角太壮观 环球热文

- 因为AI 让80%的职业原画师下岗

- 自己办理深圳创业补贴难吗?创业开饭店有补贴吗深圳

- 爱驰汽车被曝经营困难:开通员工自费交社保通道 焦点热讯

- 中国取代日本成全球第一大汽车出口国 俄罗斯为最大买家|天天热门

- 每日观点:当日快讯:沙特外交大臣表示阿拉伯国家将继续在俄乌冲突中维持中立

- 环球短讯!近视可用 特步0~700度专业大框泳镜狂促:12元包邮

- 店员称衣服掉地上摔个洞需赔款:最终结果让网友不淡定 速看

- 如何保存新鲜活虾 活虾怎么保存? 全球即时看

- 全球微动态丨体验阿斯顿·马丁DBX707 看看超跑品牌是怎么做SUV的

- 比亚迪首家全品牌体验中心开业:几万块到一百万的车全都有 当前简讯

- 第一批升级iOS 16.5正式版的用户被坑了!_要闻速递

- 又有基金公司宣布:APP停止运营!_环球快看

- 清华大学女生获选美冠军 网友:全方位优秀

- 年轻人第一辆后驱SUV 长安深蓝S3预售:16.99万起-热议

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

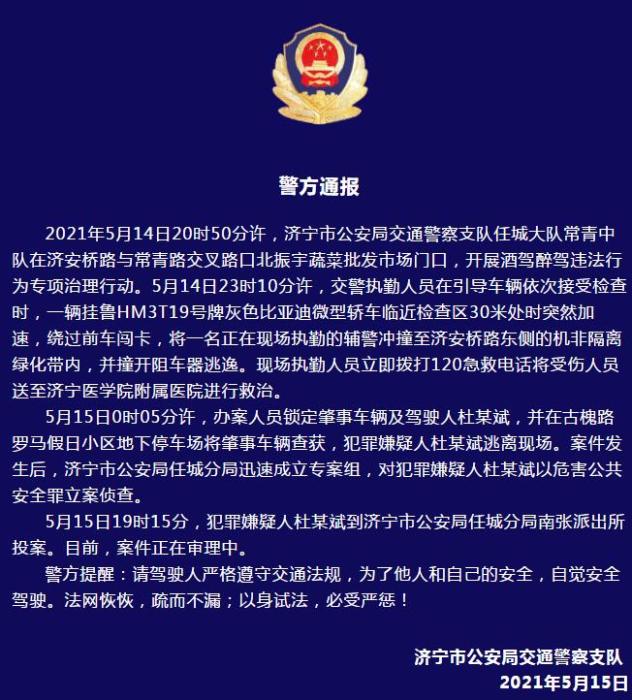

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

04-多路选择器

(资料图片)

(资料图片)

1.多路选择器

- 组合逻辑是Verilog设计中的一个重要组成部分,从电路本质上讲,组合逻辑电路的特点是输出信号只是当前时刻输入信号的函数,与其他时刻的输入状态无关,无存储电路,也没有反馈电路组合逻辑电路输出信号的电平变化仅仅与输入信号的电平变化有关,不涉及信号跳变沿的处理

- 多路选择器,是数据选择器的别称,在多路数据传送过程中,能够根据需要将其中任意一路选择出来的电路,叫做数据选择器,也称作是多路选择器或者多路开关

2.二选一选择器

- 输入两信号,在选择信号为高的时候输出第一个信号,选择信号为低的时候输出第二个信号

- 在开发板上使用KEY1,KEY2作为两个信号输入,KEY3作为信号的选择,LED灯为输出

3.FPGA设计

框图与波形图

- in_1和in_2信号是随机的

RTL

module mux2_1( input wire [0:0] in_1, input wire in_2, input wire sel, output reg out); // always产生组合逻辑的时候使用* always@(*) if(sel == 1"b1) out <= in_1; else out <= in_2;endmodule- 创建quartus项目,添加verilog代码,编译文件

testbench编写

`timescale 1ns/1nsmodule tb_mux2_1(); reg in_1; reg in_2; reg sel; wire out; initial begin in_1 <= 1"b0; in_2 <= 1"b0; sel <= 1"b0; end always #10 in_1 <= {$random} % 2; always #10 in_2 <= {$random} % 2; always #10 sel <= {$random} % 2; initial begin $timeformat(-9,0,"ns",6); //-9表示以ns的时间显示时间 10^-9表示ns,10^-3表示ms // 0表示小数点后打印的位数 // 最小显示位数6个 $monitor("@time %t:in_1=%b in2=%b out=%b",$time,in_1,in_2,out); // %t 是时间的占位符 $time使用%t占位 end // 例化module mux2_1 mux2_1_inst( .in_1 (in_1), .in_2 (in_2), .sel (sel ), .out (out ) );endmodule- 在quartus中添加仿真文件

- 设置仿真格式

- 在modelsim中进行仿真

// 其他方式实现// 方式2always@(*) case(sel) 1"b1:out = in_1; 1"b0:out = in_2; default : out = in1; endcase// 方式3assign out = sel ? in_1 : in_2;关键词:

-

-

-

-

04-多路选择器

快报:我国南海发现两处古代沉船

我国深海考古重大进展!首次发现大型古代沉船:水下第一视角太壮观 环球热文

因为AI 让80%的职业原画师下岗

帮助Linux管理员简化任务并实现自动化的七大工具

自己办理深圳创业补贴难吗?创业开饭店有补贴吗深圳

爱驰汽车被曝经营困难:开通员工自费交社保通道 焦点热讯

中国取代日本成全球第一大汽车出口国 俄罗斯为最大买家|天天热门

React闭包陷阱

每日观点:当日快讯:沙特外交大臣表示阿拉伯国家将继续在俄乌冲突中维持中立

全球快报:【财经分析】全球贸易增长正在恢复 应继续加强多边贸易合作

环球短讯!近视可用 特步0~700度专业大框泳镜狂促:12元包邮

店员称衣服掉地上摔个洞需赔款:最终结果让网友不淡定 速看

如何保存新鲜活虾 活虾怎么保存? 全球即时看

全球微动态丨体验阿斯顿·马丁DBX707 看看超跑品牌是怎么做SUV的

比亚迪首家全品牌体验中心开业:几万块到一百万的车全都有 当前简讯

第一批升级iOS 16.5正式版的用户被坑了!_要闻速递

学系统集成项目管理工程师(中项)系列23b_信息系统集成及服务管理(下)

【爬虫数据集】滇西小哥YouTube频道TOP10热门视频的热评数据,共2W条!_世界速看料

又有基金公司宣布:APP停止运营!_环球快看

清华大学女生获选美冠军 网友:全方位优秀

年轻人第一辆后驱SUV 长安深蓝S3预售:16.99万起-热议

全球信息:雨前高山春鲜 谢裕大珍珠绿茶60克到手29元

万达集团紧急声明!

03-点亮LED灯

热搜第一!BLG晋级 LPL提前锁定MSI三连冠 每日信息

全面了解华为全屋智能4.0:体验质变 最新快讯

母亲5点帮女儿排队领证结果走错地方:白排了一个小时队

当前快看:河海大学与华中师范大学签署战略合作协议

无论多少次,还是会为粉色疯狂心动!!!

文心一言 VS 讯飞星火 VS chatgpt (19)-- go语言的slice和rust语言的Vec的扩容流程是什么? 世界热文

阴阳师×GARNiDELiA决定展开合作 或为《极乐净土》高清重制版

索尼宣布将与WNBA达成合作伙伴关系 探索各种营销机会

环球今亮点!年终工作总结会议流程_年终工作总结会议通知

NASA发出警告称巨型小行星正在接近地球 大小为纽约地标自由女神像的两倍

网易旗下Jackalope Games宣布更名 正在开发一部基于“战锤”IP的游戏

苹果App商城现已有178万个应用程序 为有意义的统计数据

,影片《人生路不熟》票房突破9亿元大关 由马丽与乔杉等人主演

电视剧《仙剑奇侠传六》官微发布新海报 由许凯和虞书欣担任

顺丰控股公布4月快递物流业务经营 业务量同比增长29.59%

差价上千元该怎么选?13代酷睿i5和i7实测性能对比

华为把屏幕边框做到了1mm!畅享60 Pro即将开卖:1499元

国网东营供电公司开展全市电力设施和电能保护集中宣传活动

从350nm升到4nm 25年来AMD CPU性能已提升910倍

女子动车上提醒男子小声打电话被怼:你凭什么说我

520当天一女子逼停汽车泼粥骂渣男引围观:网友吐槽不该糟蹋粮食

由于半导体消费持续低迷 三星半导体将推迟平泽工厂4nm生产线设备投资

2023年DPC中国联赛夏季赛开战 Aster战队首秀大放异彩赢得首胜

阅读笔记:Sybilla DLT任务重启判定系统 焦点快看

首款天玑9200旗舰!vivo X90降价:256GB版3799元到手

网红三千哥直播PK饮酒过量去世 友人:喝了至少四瓶|当前通讯

英伟达RTX 4060 Ti显卡降临:关键参数已曝光 就差价格了

初三下册月考复习:第二单元知识点-天天快播报

Java生成二维码及条形码工具

python中的装饰器原理和作用 焦点热议

23款奔驰GLC评测_全球观焦点

有你家吗?杭州人均存款达16万元:全国住户存款最强8大城市 每日消息

华为笔记本性能怪兽!MateBook 16s下周首销:i7+1TB仅7999元 全球即时看

今日精选:20年来x86巨变 Intel将精简CPU架构:转向纯血64位

女子为骗男友结婚定制美颜假身份证引热议:网友感慨太假太美了 焦点报道

情侣筷子卖22元单身筷1元 超市:已下架-环球看点

双鸭山市气象台发布大风蓝色预警【IV级/一般】【2023-05-20】 全球热文

每日看点!Natasha 插件化之dll

天天最资讯丨暴雪又搞砸了 老外批《守望先锋2》太失败:浪费4年开发

桌面RTX 4070玩游戏 显示器选2K还是4K?来看对比实测 全球热推荐

远离元宇宙后 扎克伯格财富暴涨3000亿 全球最多!|全球新视野

小米两大技术接入联发科平台!卢伟冰:天玑芯片影像蜕变

37岁姐姐跟98年男友520领证 网友:羡慕了 天天讯息

全球观察:直通车是什么快递_直通车是什么

虎书 第一章 图形流水线_环球焦点

10.998万元 春风1250TR-G摩托价格公布:用上75°V型双缸发动机

焦点速看:丰田再批电动车毫无意义:烧煤发电不环保 氢燃料才合理

【环球时快讯】瓦伦丁·迪奥曼德_关于瓦伦丁·迪奥曼德介绍

C++ Today01

Kafka未触发消费异常排查实录-全球实时

基于python实现-根据Excel表格指定的UniqueKey的顺序-到另一个参考表格中查找-补全与自己相关的数据

Revit二次开发实战

天天观察:年轻人发完红包看电影 520单日总票房超1.5亿:速激10位列第一

网吧用“蛤蟆”、“天鹅”区分男女厕所 网友点赞直呼有才:官方回应

樱桃自由了!水果贵族樱桃一斤直降30元 六七月份还会继续降

B站CEO陈睿:年轻人爱学习 超8成985、211学生是B站用户 天天速递

三星独占结束!国产手机将用上“鸡血版”二代骁龙8-当前视点

浏阳:残疾人以“武”会友,散发的是自信和快乐-全球资讯

OPEN AI角色插件通道开放接入支持各种细分领域对话场角色景模型一键接入AI 智能 聚焦

记录--Vue中如何导出excel表格

马斯克回避的赛道蔚来进军了:可控核聚变20年内商用_环球热点

首发联发科8200-Ultra!小米Civi 3跑分出炉|全球即时

新疆乌鲁木齐达坂城姑娘特色农产品展示中心预计7月投用|当前速讯

网约车拒违停 2乘客赖车上超24小时还原地撒尿 官方通报:行拘-新要闻

告别MMO手游氪金!《逆水寒》手游公测预告片发布:6月30日见

黄百鸣谈为何拍《叶问5》:前几部成绩好 甄子丹也想拍 天天报道

李荣浩沉迷《王国之泪》 吐槽吉波得女王太难:不可能有人打的过 世界速递

环球快看:Revit二次开发 知识点总结(表格)

环球今亮点!荣耀:再见了,高价低配!骁龙8+芯片+IMX800仅2599元

老车主退10万差价业界良心!极狐阿尔法S HI先行版上市:32.98万_世界观速讯

微信开放520元红包:特别的爱也可以是最多1000元 世界简讯

当前要闻:synopsys dw_axi_dmac 使用集成经验

直播源码技术控制直播稳定之消息篇

全新一代华为海思芯片V811首发!七大绝技 支持8K30Hz解码-每日简讯

明道回应与蒋雯丽拍戏争议 姐弟恋新剧《转角之恋》口碑翻车:网友直呼辣眼|当前关注