最新要闻

- 哥伦比亚发布橙色预警!这座火山,或在未来几天喷发?曾致超2.3万人死亡

- 今日聚焦!建议友商跟进!长安深蓝豪送大礼:已提车用户享终身整车质保

- 热点在线丨专家:发展电车一年可节约500亿美元石油进口、这钱拿来干什么不好

- 天天观点:送给老师的便宜小礼物

- 理想杀疯了!3月交付破2万辆 成新势力新老大 李想:30-50万SUV市场占比已接近20%

- 讯息:波兰蠢驴营收向好

- 世界今日讯!斗罗大陆游戏激活码有哪些(斗罗大陆游戏激活码是多少)

- 环球快资讯丨iPhone大面积bug:苹果自带天气崩了 无任何数据

- 环球实时:国产PCSK9抑制剂 ,即将迎来商业爆发?

- 全球观速讯丨韩国主持人流鼻血仍淡定直播 本人回应没事:网友看笑但直呼真敬业

- 热文:钟南山亲自颁发!理想L9获颁“五星健康车”:383.4分创造历史

- 全球热头条丨文峰股份:3月31日融券卖出5300股,融资融券余额1.56亿元

- 加满一箱油少花13元!油价迎今年来最大降幅

- 天天热资讯!2020广州大佛寺中秋佳节拜月法会安排一览

- 汉唐元三车齐发!比亚迪乘用车在西班牙正式开售

- 【世界独家】不虚标!比亚迪汉EV冠军版实测光电续航达成率93.1%

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

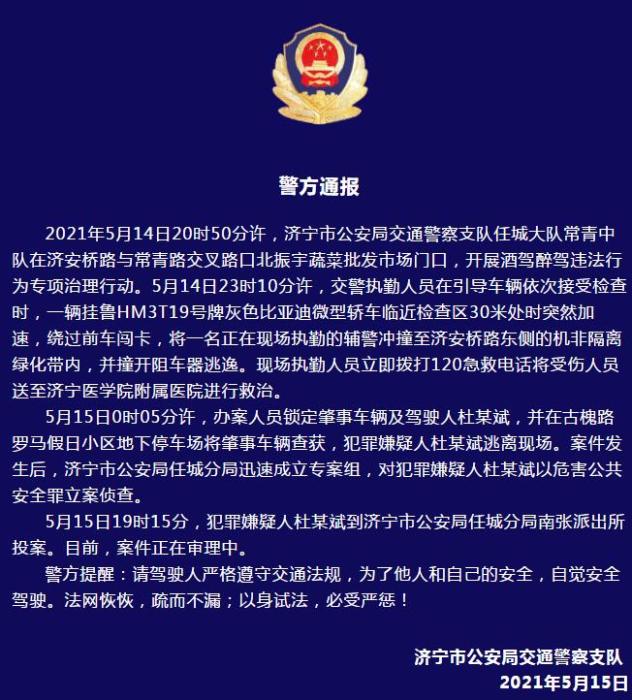

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

全球热资讯!基于zynq的OV5640摄像头的sobel算子边缘检测

最近鸽了挺久的,因为最近要做课设,再加上被这个工程的调试给难到了。在做该工程的时候,有一个良好的项目管理习惯会让开发的时候不会让人那么的高血压。特别要注意的是,异步FIFO的读写时钟的速率匹配问题,这个问题卡了我好久。

【资料图】

【资料图】

1、sobel算子

Sobel 算法是像素图像边缘检测中最重要的算子之一,在机器学习、数字媒体、计算机视觉等信息科技领域起着举足轻重的作用。在技术上,它是一个离散的一阶差分算子,用来计算图像亮度函数的一阶梯度之近似值。在图像的任何一点使用此算子,将会产生该点对应的梯度矢量或是其法矢。Sobel 边缘检测通常带有方向性,可以只检测竖直边缘或垂直边缘或都检测。实现步骤:第一步:Sobel 提供了水平方向和垂直方向两个方向的滤波模板。设 x 方向和 y 方向的卷积因子分别为 Gx和 Gy,模板如下所示,A 为原图像。第二步:矩阵运算后,就得到横向灰度值 Gx 和纵向灰度值 Gy,然后通过如下公式进行计算出该点的灰度值:这个运算比较复杂,涉及到平方和开根(FPGA 不擅长),可以采用取近似值计算方法,对于最终结果影响不大第三步:设置一个阈值 threshold,对数据进行比较然后输出二值图像

2、图像灰度算法

图像数据中,含有RGB三种颜色的数据,如果一起处理的话,要很大的的运算量和位宽,为了减小运算量,可以将24位的RGB数据转化为8位的灰度图像。虽然丢失了一些颜色等级,但是从整幅图像的整体和局部的色彩以及亮度等级分布特征来看,灰度图描述与彩色图的描述是一致的。一般有分量法、最大值法、平均值法、加权平均法四种方法对彩色图像进行灰度化。

然后本次采用的是平均值法。

将彩色图像中的三分量亮度求平均得到一个灰度值。如下:

上式中有除法,考虑到在 FPGA 中实现除法比较的消耗资源,这里在实现前可以先做如下的近似处理。可以将上面公式乘以 3/256,这样就需要同时乘以 256/3 保证公式的正确性。公式处理过程如下:对 256/3 做近似取整处理,将 256/3 替换成 85,则公式变为如下。

这样式子中除以 256 就可以采用移位方法来处理,式子变为如下:

上面处理过程中使用是对 256/3 的近似处理,当然这里可以采用其他数据,比如512/3、1024/3、2048/3 等等,基本的原则是将平均公式法中分母的 3 替换成 2 的幂次的数,这样除法就可以使用移位的方式实现,减小 FPGA 中由于存在除法带来的资源消耗。

3、sobel算法的实现

该工程用到的算子需要三行数据才能进行,我们可以先缓存两行数据,然后接下来的输入数据加上之前缓存的两行的数据就是三行数据了,示意图如下:缓存区像移位寄存器一样,一个周期输入一个数据和输出一个数据,可以用xilinx的RAM-base Shift Register IP核来实现。但上面仅实现31的模板,要实现33的模板可在每行输出串联三组寄存器,以下是示意图:然后我们就可以取寄存器组里面的值进行Sobel 算法的实现了。

4、sobel算法模块

本模块需要

- 1个16位宽1024深度的异步FIFO

- 2个16位宽1024深度的同布FIFO

- 2个8位宽400深度RAM-base Shift Register IP核

sobel_core_v1_0.v

`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company: GDUT// Engineer: Lclone// // Create Date: 2023/03/27 22:04:23// Design Name: sobel_core// Module Name: sobel_core// Project Name: sobel_core// Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision:// Revision 0.01 - File Created// Additional Comments:// //////////////////////////////////////////////////////////////////////////////////module sobel_core_v1_0# ( parameter LINE_LENGTH = 800, //行长度 parameter LINE_NUM = 480) //场长度 ( //------系统接口--------- input m_clk, //主时钟 input rst_n, //复位信号 //------摄像头接口------- input pclk, //像素时钟 input [15:0] cam_data, //图像数据输入 input data_valid, //数据有效 //------maxis接口-------- input m_axis_tready, output reg m_axis_tvalid, output [15:0] m_axis_tdata, output reg m_axis_tlast, output m_axis_tuser ); //------------------cam_fifo的信号----------------------------- reg cam_fifo_data_rd_en; //cam_fifo 读使能 reg cam_fifo_data_rd_en_r; wire [15:0] cam_fifo_data_out; //cam_fifo读出数据 wire [ 9:0] rd_data_count; //cam_fifo读出计数 //------------------图像灰度算法的信号------------------------ wire [ 9:0] sum; reg [15:0] gray_r; wire [ 7:0] gray_8b_o; reg gray_valid; //-------------------sbole模块信号---------------------------- wire [ 7:0] filter_data_out; wire filter_data_valid; //-------------------两个同步fifo的信号----------------------- wire [15:0] fifo_data0; wire [15:0] fifo_data1; wire [ 9:0] fifo_data_count0; wire [ 9:0] fifo_data_count1; reg [ 9:0] out_data_count; reg fifo_flag; //-------------------场计数信号------------------------------- reg [ 8:0] line_cnt; reg line_end; //------------------------------------------------------------ reg m_axis_act; //m_axis活动信号 always@(posedge m_clk or negedge rst_n) begin if(rst_n == 0) cam_fifo_data_rd_en <= 0; else if(rd_data_count >= LINE_LENGTH/2)//当cam_fifo里的数据大于400个的时候,就进行读取 cam_fifo_data_rd_en <= 1; else if(rd_data_count <= 2) //当cam_fifo里的数据小于两个的时候,就暂停读取 cam_fifo_data_rd_en <= 0; else cam_fifo_data_rd_en <= cam_fifo_data_rd_en; end always @(posedge m_clk) cam_fifo_data_rd_en_r <= cam_fifo_data_rd_en; //延一拍,作为写入同步fifo的写信号 always@(posedge m_clk or negedge rst_n) begin if(rst_n == 0) m_axis_act <= 0; else if(fifo_data_count0 >= LINE_LENGTH/2 - 1 ) //当同步fifo0的数据有400个的时候就使axi_stream接口活动 m_axis_act <= 1; else if(fifo_data_count1 <= 1 )//当同步fifo1的数据小于1个的时候就使axi_stream接口暂停活动 m_axis_act <= 0; else m_axis_act <= m_axis_act; end always@(posedge m_clk) m_axis_tvalid <= m_axis_act;//延一拍作为tvalid信号与数据同步 always@(posedge m_clk or negedge rst_n) begin//每行数据的最后一个拉高tlast信号 if(rst_n == 0) m_axis_tlast <= 0; else if(out_data_count == LINE_LENGTH - 2 & m_axis_tvalid) m_axis_tlast <= 1; else m_axis_tlast <= 0; end always@(posedge m_clk or negedge rst_n) begin//场计数器,为给出帧同步信号而设置的。 if(rst_n == 0) line_cnt <= 0; else if(line_cnt == LINE_NUM - 1 & out_data_count == LINE_LENGTH - 1) line_cnt <= 0; else if(out_data_count == LINE_LENGTH - 1) line_cnt <= line_cnt + 1"b1; else line_cnt <= line_cnt; end always@(posedge m_clk or negedge rst_n) begin//输出计数器,为给出tlast,切换fifo,给出帧同步信号而设置的。 if(rst_n == 0) out_data_count <= 0; else if(out_data_count == LINE_LENGTH - 1) out_data_count <= 0; else if(m_axis_tvalid & m_axis_tready) out_data_count <= out_data_count + 1"b1; else out_data_count <= out_data_count; end always@(posedge m_clk or negedge rst_n) begin if(rst_n == 0) line_end <= 0; else if(line_cnt == LINE_NUM - 1 & out_data_count == LINE_LENGTH - 1) line_end <= 1; else line_end <= 0; end assign m_axis_tuser = (out_data_count == 0 & m_axis_tvalid & m_axis_tready & line_cnt == 0)? 1:0; //每个帧的第一个数据拉高tuser,也就是帧同步信号 //-------------------------------------------图像灰度算法------------------------------------------------------ assign sum = {cam_fifo_data_out[15:11],3"b0} + {cam_fifo_data_out[10:5],2"b0} + {cam_fifo_data_out[4:0],3"b0}; always@(posedge m_clk or negedge rst_n) begin if(rst_n == 0) gray_r <= 16"d0; else if(cam_fifo_data_rd_en_r) gray_r <= (sum << 6)+(sum << 4)+(sum << 2)+ sum; else gray_r <= 16"d0; end assign gray_8b_o = gray_r[15:8]; always@(posedge m_clk) begin gray_valid <= cam_fifo_data_rd_en_r; end //------------------------------------------同步fifo的数据切换-------------------------------------------------- always@(posedge m_clk or negedge rst_n) begin if(rst_n == 0) fifo_flag <= 0; else if(out_data_count >= LINE_LENGTH - 1) fifo_flag <= 0; else if(out_data_count >= LINE_LENGTH/2 - 1) fifo_flag <= 1; else fifo_flag <= fifo_flag; end assign m_axis_tdata = (fifo_flag) ? fifo_data1 : fifo_data0; //---------------------------------------------------------------------------------------------------------- fifo_generator_1 cam_data_fifo ( .rst(~rst_n), // input wire rst .wr_clk(pclk), // input wire wr_clk .rd_clk(m_clk), // input wire rd_clk .din(cam_data), // input wire [15 : 0] din .wr_en(data_valid), // input wire wr_en .rd_en(cam_fifo_data_rd_en), // input wire rd_en .dout(cam_fifo_data_out), // output wire [15 : 0] dout .full(), // output wire full .empty(), // output wire empty .rd_data_count(rd_data_count), // output wire [9 : 0] rd_data_count .wr_rst_busy(), // output wire wr_rst_busy .rd_rst_busy() // output wire rd_rst_busy); fifo_generator_0 fifo_generator_0_inst ( .clk(m_clk), // input wire clk .srst(~rst_n), // input wire srst .din(cam_fifo_data_out), // input wire [15 : 0] din .wr_en(cam_fifo_data_rd_en_r), // input wire wr_en .rd_en(~fifo_flag & m_axis_act & m_axis_tready), // input wire rd_en .dout(fifo_data0), // output wire [15 : 0] dout //m_axis_tdata .full(), // output wire full .empty(), // output wire empty .data_count(fifo_data_count0) // output wire [9 : 0] data_count);sobel_filter#( .DATA_WIDTH(8))sobel_filter_inst( .clk(m_clk), .reset_p(~rst_n), .data_in(gray_8b_o), .data_in_valid(gray_valid), .data_in_hs(1"b1), .data_in_vs(1"b1), .threshold(8"d127), //-------------------------- .data_out(filter_data_out), .data_out_valid(filter_data_valid), .data_out_hs(), .data_out_vs() ); fifo_generator_0 fifo_generator_1_inst ( .clk(m_clk), // input wire clk .srst(~rst_n), // input wire srst .din({{5{filter_data_out[0]}},{6{filter_data_out[0]}},{5{filter_data_out[0]}}}),// input wire [15 : 0] din .wr_en(filter_data_valid), // input wire wr_en .rd_en(fifo_flag & m_axis_act & m_axis_tready), // input wire rd_en .dout(fifo_data1), // output wire [15 : 0] dout .full(), // output wire full .empty(), // output wire empty .data_count(fifo_data_count1) // output wire [9 : 0] data_count);endmodulesobel_filter.v

`timescale 1ns / 1psmodule sobel_filter#( parameter DATA_WIDTH = 8)( input clk, input reset_p, input [DATA_WIDTH - 1:0] data_in, input data_in_valid, input data_in_hs, input data_in_vs, input [DATA_WIDTH - 1:0] threshold, //-------------------------- output reg [DATA_WIDTH - 1:0] data_out, output data_out_valid, output data_out_hs, output data_out_vs ); reg [DATA_WIDTH - 1:0] row0_col0; reg [DATA_WIDTH - 1:0] row0_col1; reg [DATA_WIDTH - 1:0] row0_col2; reg [DATA_WIDTH - 1:0] row1_col0; reg [DATA_WIDTH - 1:0] row1_col1; reg [DATA_WIDTH - 1:0] row1_col2; reg [DATA_WIDTH - 1:0] row2_col0; reg [DATA_WIDTH - 1:0] row2_col1; reg [DATA_WIDTH - 1:0] row2_col2; wire [DATA_WIDTH - 1:0] line0_data; wire [DATA_WIDTH - 1:0] line1_data; wire [DATA_WIDTH - 1:0] line2_data; reg data_in_valid_dly1; reg data_in_valid_dly2; reg data_in_valid_dly3; reg data_in_hs_dly1; reg data_in_hs_dly2; reg data_in_hs_dly3; reg data_in_vs_dly1; reg data_in_vs_dly2; reg data_in_vs_dly3; wire Gx_is_positive; wire Gy_is_positive; reg [DATA_WIDTH+1:0] Gx_absolute; //high bit expansion 2bit reg [DATA_WIDTH+1:0] Gy_absolute; //high bit expansion 2bit always @(posedge clk or posedge reset_p) begin if(reset_p) begin row0_col0 <= "d0; row0_col1 <= "d0; row0_col2 <= "d0; row1_col0 <= "d0; row1_col1 <= "d0; row1_col2 <= "d0; row2_col0 <= "d0; row2_col1 <= "d0; row2_col2 <= "d0; end else if(data_in_hs && data_in_vs) if(data_in_valid) begin row0_col2 <= line0_data; row0_col1 <= row0_col2; row0_col0 <= row0_col1; row1_col2 <= line1_data; row1_col1 <= row1_col2; row1_col0 <= row1_col1; row2_col2 <= line2_data; row2_col1 <= row2_col2; row2_col0 <= row2_col1; end else begin row0_col2 <= row0_col2; row0_col1 <= row0_col1; row0_col0 <= row0_col0; row1_col2 <= row1_col2; row1_col1 <= row1_col1; row1_col0 <= row1_col0; row2_col2 <= row2_col2; row2_col1 <= row2_col1; row2_col0 <= row2_col0; end else begin row0_col0 <= "d0; row0_col1 <= "d0; row0_col2 <= "d0; row1_col0 <= "d0; row1_col1 <= "d0; row1_col2 <= "d0; row2_col0 <= "d0; row2_col1 <= "d0; row2_col2 <= "d0; end end always @(posedge clk) begin data_in_valid_dly1 <= data_in_valid; data_in_valid_dly2 <= data_in_valid_dly1; data_in_valid_dly3 <= data_in_valid_dly2; data_in_hs_dly1 <= data_in_hs; data_in_hs_dly2 <= data_in_hs_dly1; data_in_hs_dly3 <= data_in_hs_dly2; data_in_vs_dly1 <= data_in_vs; data_in_vs_dly2 <= data_in_vs_dly1; data_in_vs_dly3 <= data_in_vs_dly2;endassign data_out_valid = data_in_valid_dly3;assign data_out_hs = data_in_hs_dly3;assign data_out_vs = data_in_vs_dly3; shift_register_2taps #( .DATA_WIDTH (DATA_WIDTH) )shift_register_2taps_inst ( .clk (clk), .shiftin (data_in), .shiftin_valid (data_in_valid), .shiftout (), .taps1x (line1_data), .taps0x (line0_data) );assign line2_data = data_in;//----------------------------------------------------// mask x mask y//[-1,0,1] [ 1, 2, 1]//[-2,0,2] [ 0, 0, 0]//[-1,0,1] [-1,-2,-1]//----------------------------------------------------assign Gx_is_positive = (row0_col2 + row1_col2*2 + row2_col2) >=(row0_col0 + row1_col0*2 + row2_col0);assign Gy_is_positive = (row0_col0 + row0_col1*2 + row0_col2) >=(row2_col0 + row2_col1*2 + row2_col2);always @(posedge clk or posedge reset_p) begin if(reset_p) Gx_absolute <= "d0; else if(data_in_valid_dly1) begin if(Gx_is_positive) Gx_absolute <= (row0_col2 + row1_col2*2 + row2_col2) - (row0_col0 + row1_col0*2 + row2_col0); else Gx_absolute <= (row0_col0 + row1_col0*2 + row2_col0) - (row0_col2 + row1_col2*2 + row2_col2); endendalways @(posedge clk or posedge reset_p) begin if(reset_p) Gy_absolute <= "d0; else if(data_in_valid_dly1) begin if(Gy_is_positive) Gy_absolute <= (row0_col0 + row0_col1*2 + row0_col2) - (row2_col0 + row2_col1*2 + row2_col2); else Gy_absolute <= (row2_col0 + row2_col1*2 + row2_col2) - (row0_col0 + row0_col1*2 + row0_col2); endend//----------------------------------------------------//result//----------------------------------------------------always @(posedge clk or posedge reset_p) begin if(reset_p) data_out <= 1"b0; else if(data_in_valid_dly2) begin data_out <= ((Gx_absolute+Gy_absolute)>threshold) ? 1"b0 : 1"b1; endendendmodule5、仿真

仿真过程有复杂,调了许久,这里暂不写出。

6、上板验证

本次还是在小梅哥的OV5640_TFT这个工程的基础上进行修改,并将上面提到的模块打包成IP核,在block design里进行链接。

(1)删除红框内的模块

(2)修改OV5640_data_0 IP核

module OV5640_Data_v1_0( Rst_n, //复位 PCLK, //像素时钟 Vsync, //场同步信号 Href, //行同步信号 Data, //数据 DataValid, //数据有效信号 DataPixel, //像素数据 Frame_Clk //时钟信号); input Rst_n; //复位 input PCLK; //像素时钟 input Vsync; //场同步信号 input Href; //行同步信号 input [7:0]Data; //数据 output DataValid; //数据有效信号 output [15:0]DataPixel; //像素数据 output Frame_Clk;//时钟信号 reg r_Vsync; reg r_Href; reg [7:0]r_Data; reg [15:0]r_DataPixel; reg r_DataValid; reg [12:0]Hcount; reg [11:0]Vcount; reg [3:0]FrameCnt; reg Dump_Frame; assign DataPixel = Dump_Frame ? r_DataPixel : 24"d0; assign DataValid = Hcount[0] & Dump_Frame; //摄像头时钟使能 //assign Frame_Ce = ((Hcount[0]) || (!r_Href)) & Dump_Frame;//1"b1;//(r_DataValid & Dump_Frame)||(!r_DataValid); //assign Frame_Ce = ((!Hcount[0]) || (!r_Href)) & Dump_Frame;//1"b1;//(r_DataValid & Dump_Frame)||(!r_DataValid); //时钟为像素时钟 assign Frame_Clk = PCLK; //打拍 always@(posedge PCLK) begin r_Vsync <= Vsync; r_Href <= Href; r_Data <= Data; end //行同步信号为1时,行计数器加一(行同步信号为0时归零) always@(posedge PCLK or negedge Rst_n) if(!Rst_n) Hcount <= 0; else if(r_Href) Hcount <= Hcount + 1"d1; else Hcount <= 0; //8位转16位,赋予像素数据 always@(posedge PCLK or negedge Rst_n) if(!Rst_n) r_DataPixel <= 0; else if(~Hcount[0]) r_DataPixel <= {r_Data,Data}; else r_DataPixel[7:0] <= r_Data; //产生数据有效信号 always@(posedge PCLK or negedge Rst_n) if(!Rst_n) r_DataValid <= 0; else if(Hcount[0] && r_Href) r_DataValid <= 1; else r_DataValid <= 0; //行同步信号由0变为1时,列计数器加一(场同步信号为1时归零) always@(posedge PCLK or negedge Rst_n) if(!Rst_n) Vcount <= 0; else if(r_Vsync) Vcount <= 0; else if({r_Href,Href} == 2"b01) Vcount <= Vcount + 1"d1; else Vcount <= Vcount; //场同步信号由0变为1时,帧计数加一,最大为10 always@(posedge PCLK or negedge Rst_n) if(!Rst_n) FrameCnt <= 0; else if({r_Vsync,Vsync}== 2"b01)begin if(FrameCnt >= 10) FrameCnt <= 4"d10; else FrameCnt <= FrameCnt + 1"d1; end else FrameCnt <= FrameCnt; //当计数大于等于10帧时,Dump_Frame变为1,否则为0 always@(posedge PCLK or negedge Rst_n) if(!Rst_n) Dump_Frame <= 0; else if(FrameCnt >= 10) Dump_Frame <= 1"d1; else Dump_Frame <= 0;endmodule(3)添加打包好的IP核,并建立连接

(4)修改SDK中的文件

将红框中的寄存器的值改为图片所示的值。即使摄像头输出400*480的图像。

最后烧入程序,可观察到如下结果

7、可改进的地方

可以加个按键来控制sobel算法里的阈值。

(该随笔部分介绍来自小梅哥的教材,侵权删。)

关键词:

-

-

天天新动态:小米路由器3C刷入Breed和OpenWrt

本文链接:https: www cnblogs com snoopy1866 p 17278237 html准备工具:小米路由器3C(R3L)...

来源: -

-

全球快播:相同基准点的多个rvt BIM模型数据配准后位置有错位偏差问题处理

场景:提供的bim模型数据包含多个rvt格式数据,这些数据具有相同的基准点,如:在使用ArcGISPro处理了其...

来源: 全球热资讯!基于zynq的OV5640摄像头的sobel算子边缘检测

天天新动态:小米路由器3C刷入Breed和OpenWrt

【世界播资讯】Microsoft Visual Studio 2022 透明背景设置

全球快播:相同基准点的多个rvt BIM模型数据配准后位置有错位偏差问题处理

哥伦比亚发布橙色预警!这座火山,或在未来几天喷发?曾致超2.3万人死亡

今日聚焦!建议友商跟进!长安深蓝豪送大礼:已提车用户享终身整车质保

热点在线丨专家:发展电车一年可节约500亿美元石油进口、这钱拿来干什么不好

天天观点:送给老师的便宜小礼物

头条焦点:Redis——内存淘汰策略

理想杀疯了!3月交付破2万辆 成新势力新老大 李想:30-50万SUV市场占比已接近20%

讯息:波兰蠢驴营收向好

世界今日讯!斗罗大陆游戏激活码有哪些(斗罗大陆游戏激活码是多少)

全球今日报丨Java 基础 -- NIO 多人聊天室

环球热推荐:四元数法

环球快资讯丨iPhone大面积bug:苹果自带天气崩了 无任何数据

shell 脚本之一键部署安装 Nginx

环球实时:国产PCSK9抑制剂 ,即将迎来商业爆发?

全球观速讯丨韩国主持人流鼻血仍淡定直播 本人回应没事:网友看笑但直呼真敬业

热文:钟南山亲自颁发!理想L9获颁“五星健康车”:383.4分创造历史

全球热头条丨文峰股份:3月31日融券卖出5300股,融资融券余额1.56亿元

全球动态:读SQL进阶教程笔记04_集合运算

加满一箱油少花13元!油价迎今年来最大降幅

天天热资讯!2020广州大佛寺中秋佳节拜月法会安排一览

Swift与OC混编

环球信息:知乎使用指南

汉唐元三车齐发!比亚迪乘用车在西班牙正式开售

【世界独家】不虚标!比亚迪汉EV冠军版实测光电续航达成率93.1%

世界今热点:中国最畅销手机出炉:“十三香”传奇上演 安卓高端难成

内存狂魔第一次冲上8200MHz!芝奇带来96GB DDR5

佛山企业标准“领跑者”数量连续三年全国第一

当前视点!腮腺炎初期有什么症状?_腮腺炎初期有什么症状

全球时讯:深度学习——用简单的线性模型构建识别鸟与飞机模型

Redhat/CentOS Linux 系统进入单用户模式

天天即时看!万恶的环境 二 java

今日要闻!验证码被攻破!谷歌AI已能精准识别 GPT-4则装瞎求人帮忙

美女博主在家拍擦边视频?穿瑜伽服涨粉百万!真相是...

全球今头条!3DMark加入AMD FSR专项测试:终于追上NVIDIA、Intel

全球报道:广汽埃安AION Y Plus 2023款上市:14万级唯一纯电610KM续航

天天信息:V观财报|科达制造股东广东联塑短线交易致歉

世界消息!Teamcenter_SOA开发:使用查询构建器查询数据

即时:flatMap

热讯:React Native 备忘清单_开发速查表分享

世界信息:5.98万起售还嫌贵?五菱缤果上市即热销:当天交付522台

每日热议!想买车的抓紧 广州新能源汽车也有补贴了:最高1万元

世界微头条丨《原神》开发商新作:米哈游《崩坏:星穹铁道》预约超2000万

环球热推荐:米香四溢:袁隆平品牌隆平农场东北晶米10斤39.9元发车

华硕ROG游戏手机7真机曝光:无挖孔全面屏、后置三摄

天天讯息:华天科技2022年营收119亿元 拟实施先进封测研发及产业化项目

当前焦点!Leetcode Practice --- 栈和队列

我的第一个项目(七):(解决问题)Vue中canvas无法绘制图片

观点:确认引进内地!《小美人鱼》新泄露镜头:爱丽儿深情抚摸王子的脸

全球首个商用海底数据中心在海南下水:算力高、散热不费电

今日关注:不挑路面、转得很稳 仰望U8如何实现原地掉头?官方详解

大学生应聘饭店洗碗工被HR婉拒 HR:第一份工作很重要 这会害了他

不等发布会!vivo X Fold2真机抢先看:素皮+玻璃设计惊艳

现场丨圆桌对话:抓住确定性——楼宇经济的大周期和小趋势

讯息:awk 处理 Git 提交信息生成 Release Note

最长上升子序列 II

视焦点讯!day3 函数的定义和调用,练习编写简单的程序(记录1)

天天热文:内存/SSD白菜价甩卖 美光芯片大减产:工厂停机率创纪录

任泽平:在中国做生意没任何理由抱怨 燃油车正迎来诺基亚时刻

世界新资讯:宏碁推出W系列4K电视:QLED面板、30W扬声器

油价“二连降” 今年来最大降幅!加满一箱油少花13元

【全球热闻】网络时钟同步设备(NTP时间同步服务器)技术设计应用方案

全球实时:记录--你可能忽略的10种JavaScript快乐写法

聚焦:无所畏惧的求和题解

今亮点!商品日报(3月31日):焦炭低位反弹菜油补涨 纸浆、玻璃主力合约跌超2%

保姆级教程!12306官方详解“免费坐高铁”

环球速递!RTX 40系显卡才能“撑得住”!《赛博朋克2077》实现路径光追

夏季必备 圈叉潮品纯棉印花T恤/短裤24.9元起

【新视野】编程神童立志写最棒的程序改变世界 严重偏科只能选职高 妈妈无奈

世界视讯!成龙自豪发声:不是我要去好莱坞 而是好莱坞要我

“19鑫苑01”到期日期将延期一年

Excel批量检查5列数据是否一致(存在不规则空值)

【密码管理器】上海道宁为您提供存储和使用强密码的简单方法工具软件——1Password

【环球报资讯】MQTT协议介绍

世界热资讯!开心档之Go 语言环境安装

DIM中的一些知识点(慢更)

新消息丨每日机构分析:3月31日

全球实时:国家发展改革委:国内汽、柴油价格每吨分别降低335元和320元

焦点简讯:吃日料、听京剧 库克时隔3年再访中国:6年前还去过ofo小黄车总部

全球观焦点:酷派新品发布会定档4月3日:三款新机待发

世界聚焦:2023增长最快的手机品牌!一加Ace 2首销日销量在第三方平台遥遥领先

天天观察:B站弹幕射击《爆裂魔女》5月30日停运 共运营592天

任天堂Switch 2不会远了!开发者已收到新主机开发工具

世界信息:周日阳光可期抓紧洗晒 下周四冷空气再袭降水将达到中雨

每日快讯!卸载SQL Server 2012图文教程

环球报道:你还在手写 join 联表查询?MyBatis-Plus 这样写太香了!

天天新动态:Python 数字类型之 int float

每日观点:收评:两市红盘震荡创指涨0.69% 人工智能板块涨幅居前

世界百事通!比亚迪F品牌再曝谍照 主攻40-60万市场/下半年预售

天天资讯:38岁985文科硕士被迫送外卖!本人再发声:已脱下孔乙己长衫 应聘道士被拒

云南一县城禁止“脏车入城”:有明显污迹、车轮粘泥不许在城区行驶

百元就能畅享8K 流畅清爽无广告!当贝盒子H3视频评测

当前快讯:刘浩存在新片《龙马精神》首映礼上哭了:感谢成龙带自己拍戏

环球今头条!GPT-4被指威胁公共安全!OpenAI遭第三方组织投诉

基于Go/Grpc/kubernetes/Istio开发微服务的最佳实践尝试 - 2/3

【焦点热闻】如何实现根据环境切换不同配置?

数据丢失不用怕,火山引擎 DataLeap 提供排查解决方案

英特尔以强大产品力,迎接生成式AI的广阔机遇