最新要闻

- 【世界聚看点】国产DDR5价格屠夫 金百达32GB 6400MHz内存999元(CL32低延迟)

- 两人合作小品成春晚亮点 马丽回应离开沈腾就不行了:我俩都是1

- 春节看哪部电影?雷军没选《流浪地球2》 听网友的看了《无名》

- 易烊千玺主演电影票房破150亿:新片《满江红》正在热映

- 春节警惕“节日病”:过度饮酒易引发胰腺疾病

- 【报资讯】气温最低零下53℃ 大兴安岭女子回家发现单元门冻成冰窖

- 环球最资讯丨时隔3年 一加将再发概念机:搭载颠覆性技术

- 全球播报:吴孟达再现《流浪地球2》引热议 网友:看到达叔泪目

- 热点在线丨曝iPhone 15 Pro屏幕边框收窄:全系都是灵动岛设计

- 资讯推荐:漠河零下53℃是什么体验?冻梨能把板砖敲稀碎

- 带薪撸猫!95后宠托师春节保底收入过万:工作氛围很轻松

- 最长已经12年了!聊聊那些龟速进步的笔记本电脑部件

- 全球消息!今晚停服!网易发布致暴雪国服玩家的告别信:会服务到最后一刻

- 当前热讯:小米2023年安卓之光!小米13 Ultra现身:1英寸徕卡影像之王预定

- 世界新消息丨黑鲨唯一在售机型!黑鲨5 RS京东有货:2499元

- 全球热推荐:不过兔年过猫年 越南也有春晚 网友:有VCD卓依婷那味了

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

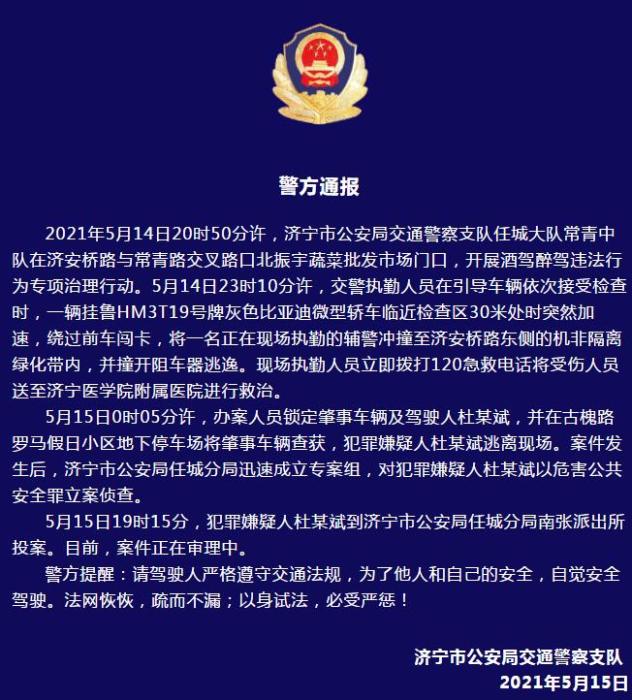

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

世界新动态:通用8位SPI接口模块——verilog实现

(相关资料图)

(相关资料图)

本次设计一个八位的SPI的接口模块,可以修改输出的频率,也可以通过修改参数来设置通信模式。本模块是设定生成一个目标输出频率的二倍计数器,然后通关计数的值来输出响应的信号,从而进行SPI通信。本模块既可以发送数据也可以接收数据,给Send_en信号使开始发送数据,在接收到8位数据后会生成Read_en信号。片选信号只设定了1位,但是可以通过简单的修改位宽来设置多位。

一、模块代码

`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company: // Engineer: Lclone// // Create Date: 2023/01/23 00:56:52// Design Name: SPI_Interface// Module Name: SPI_Interface// Project Name: // Target Devices: // Tool Versions: // Description: // SPI接口模块// 可修改分频参数来生成目标频率,最低分频系数为2;// 可以置位CPOL、CPHA可以来设置通信模式;// 本模块只有1位,但是可以简单修改位宽来设置多位片选信号// Dependencies: // // Revision:// Revision 0.01 - File Created// Additional Comments:// //////////////////////////////////////////////////////////////////////////////////module SPI_Interface# ( parameter Value_divide = 2)//分频系数(最低为2) ( //-----------------内部接口------------------ input Clk, //时钟 input Rst_n, //复位信号 input CPOL, //时钟极性 input CPHA, //时钟相位 input CS_input, //片选信号 input Send_en, //发送使能 input [7:0] Data_send, //待发送数据 output reg Read_en, //接收数据读使能 output reg [7:0] Data_recive, //接收到的数据 //------------------外部接口------------------ output reg Spi_clk, //输出时钟端 output reg Spi_mosi, //主输出从接收端 input Spi_miso, //主接收从输出端 output Cs_output //片选信号输出 ); reg act_flag; //活动状态寄存器 reg [9:0] cnt_divide; //分频计数器 reg [7:0] Data_send_reg; //带发送数据寄存器 reg [4:0] cnt_pulse; //脉冲计数器 always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) act_flag <= 0; else if(Send_en == 1) act_flag <= 1; else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1 & cnt_pulse == 16) act_flag <= 0; else act_flag <= act_flag; end always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) Read_en <= 0; else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1 & cnt_pulse == 16) Read_en <= 1; else Read_en <= 0; end always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) Data_send_reg <= 0; else if(Send_en == 1) Data_send_reg <= Data_send; else cnt_divide <= 0; end always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) cnt_divide <= 0; else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1) cnt_divide <= 0; else if(act_flag == 1) cnt_divide <= cnt_divide + 1"b1; else cnt_divide <= 0; end always @(posedge Clk or negedge Rst_n) begin//生成目标时钟两倍频率的的cnt_pulse if(Rst_n == 0) cnt_pulse <= 0; else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1 & cnt_pulse == 16) cnt_pulse <= 0; else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1) cnt_pulse <= cnt_pulse + 1"b1; else if(act_flag == 1) cnt_pulse <= cnt_pulse; else cnt_pulse <= 0; end always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) begin if(CPOL == 1) begin Spi_clk <= 1; Spi_mosi <= 1; Data_recive <= 0; end else begin Spi_clk <= 0; Spi_mosi <= 1; Data_recive <= 0; end end else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1) begin if(CPHA == 0) case(cnt_pulse) 0:begin Spi_clk <= Spi_clk; Spi_mosi <= Data_send_reg[7]; Data_recive <= Data_recive; end 1:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[7] <= Spi_miso; end 2:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[6]; Data_recive <= Data_recive; end 3:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[6] <= Spi_miso; end 4:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[5]; Data_recive <= Data_recive; end 5:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[5] <= Spi_miso; end 6:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[4]; Data_recive <= Data_recive; end 7:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[4] <= Spi_miso; end 8:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[3]; Data_recive <= Data_recive; end 9:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[3] <= Spi_miso; end 10:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[2]; Data_recive <= Data_recive; end 11:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[2] <= Spi_miso; end 12:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[1]; Data_recive <= Data_recive; end 13:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[1] <= Spi_miso; end 14:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[0]; Data_recive <= Data_recive; end 15:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[0] <= Spi_miso; end 16:begin Spi_clk <= ~Spi_clk; Spi_mosi <= 1; Data_recive <= Data_recive; end default:; endcase else case(cnt_pulse) 0:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[7]; Data_recive <= Data_recive; end 1:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[7] <= Spi_miso; end 2:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[6]; Data_recive <= Data_recive; end 3:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[6] <= Spi_miso; end 4:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[5]; Data_recive <= Data_recive; end 5:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[5] <= Spi_miso; end 6:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[4]; Data_recive <= Data_recive; end 7:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[4] <= Spi_miso; end 8:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[3]; Data_recive <= Data_recive; end 9:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[3] <= Spi_miso; end 10:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[2]; Data_recive <= Data_recive; end 11:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[2] <= Spi_miso; end 12:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[1]; Data_recive <= Data_recive; end 13:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[1] <= Spi_miso; end 14:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[0]; Data_recive <= Data_recive; end 15:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[0] <= Spi_miso; end 16:begin Spi_clk <= Spi_clk; Spi_mosi <= 1; Data_recive <= Data_recive; end default:; endcase end end assign Cs_output = CS_input; endmodule二、仿真

1、仿真激励

`timescale 1ns / 1psmodule SPI_tb();reg clk_50m;initial clk_50m <= 1;always #10 clk_50m <= ~clk_50m;reg rst_n;initial begin rst_n <= 0; #200 rst_n <= 1;endreg Send_en;reg [7:0]Data_send;wire Read_en;wire [7:0]Data_recive;wire Spi_clk;wire Spi_mosi;wire Spi_miso;wire Cs_output;SPI_Interface# ( .Value_divide (4))SPI_inst ( //-----------------内部接口------------------ .Clk (clk_50m), .Rst_n (rst_n), .CPOL (1), .CPHA (0), .CS_input (1), .Send_en (Send_en), .Data_send (Data_send), .Read_en (Read_en), .Data_recive (Data_recive), //------------------外部接口------------------ .Spi_clk (Spi_clk), .Spi_mosi (Spi_mosi), .Spi_miso (Spi_miso), .Cs_output (Cs_output) );assign Spi_miso = Spi_mosi;initial begin Send_en <= 0; Data_send <= 0; #400; Send_en <= 1; Data_send <= 8"haf; #20 Send_en <= 0; #800; Send_en <= 1; Data_send <= 8"h55; #20 Send_en <= 0;endendmodule2、仿真结果

两倍分频:

四倍分频:

八倍分频:

CPOL=1、CPHA=1;

CPOL=1、CPHA=0;

CPOL=0、CPHA=0;

CPOL=0、CPHA=1;

结论:仿真实验初步成功,能够满足SPI通信的基本要求。

-

-

![【环球报资讯】[概率论与数理统计]笔记:4.2 统计量](http://img.inpai.com.cn/2022/0923/20220923110333789.jpg)

-

-

世界新动态:通用8位SPI接口模块——verilog实现

【环球报资讯】[概率论与数理统计]笔记:4.2 统计量

【世界聚看点】国产DDR5价格屠夫 金百达32GB 6400MHz内存999元(CL32低延迟)

http基础(随缘更新)

两人合作小品成春晚亮点 马丽回应离开沈腾就不行了:我俩都是1

春节看哪部电影?雷军没选《流浪地球2》 听网友的看了《无名》

易烊千玺主演电影票房破150亿:新片《满江红》正在热映

春节警惕“节日病”:过度饮酒易引发胰腺疾病

【报资讯】气温最低零下53℃ 大兴安岭女子回家发现单元门冻成冰窖

网络编程

【教程】配置多个SSH-Key

世界简讯:MySQL笔记01: MySQL入门_1.2 MySQL下载安装与配置

环球最资讯丨时隔3年 一加将再发概念机:搭载颠覆性技术

全球播报:吴孟达再现《流浪地球2》引热议 网友:看到达叔泪目

天天快播:学习笔记——Liunx中CentOS中的有关(network)的命令;其他命令;关机重启命令

天天快讯:区块链基础入门(一)

全球视点![概率论与数理统计]笔记:4.1 总体与样本

热点在线丨曝iPhone 15 Pro屏幕边框收窄:全系都是灵动岛设计

资讯推荐:漠河零下53℃是什么体验?冻梨能把板砖敲稀碎

PDF划词翻译

带薪撸猫!95后宠托师春节保底收入过万:工作氛围很轻松

最长已经12年了!聊聊那些龟速进步的笔记本电脑部件

全球消息!今晚停服!网易发布致暴雪国服玩家的告别信:会服务到最后一刻

当前热讯:小米2023年安卓之光!小米13 Ultra现身:1英寸徕卡影像之王预定

世界新消息丨黑鲨唯一在售机型!黑鲨5 RS京东有货:2499元

全球热推荐:不过兔年过猫年 越南也有春晚 网友:有VCD卓依婷那味了

天天微速讯:不锈钢保温又保冷 富光316L畅饮杯59元包邮(日常99元)

环球时讯:春节档总票房破20亿:《流浪地球2》领衔 同步冲击好莱坞

“中国造”的土耳其最快地铁正式开跑:时速120km 全自动驾驶

学习笔记——Liunx;Linux文件与目录结构;VI/VIM编辑器(一般模式、编辑模式、命令模式)

天天快播:微软Windows系统开发生变:Win10渐成弃儿 Win12呼之欲出

卷轴屏短期量产无望:困难重重

春节档破19亿 《流浪地球2》领跑:主演吴京总票房即将突破300亿

网友晒山东过年名场面:家族人共行磕头礼 仪式感拉满

iPhone 14 Pro不再是美国5G网速最快:被三星、谷歌超越

张艺谋执导!孙红雷谈《满江红》:超出预期 预测票房20亿起

【天天新要闻】曝iPad Pro明年有重大升级:玻璃材质、OLED屏幕

当前信息:今天上演2023年首场“星月童话”:肉眼可见金星、土星相伴月球

读函数式编程思维笔记04_语言与范式_模式与重用

头条:你看了吗?2023央视春晚触达110亿人次 年轻人占比过半

天天头条:气象台发布寒潮蓝色!山东断崖式降温:冷成了“山冻”

微资讯!魔兽世界国服关服最后一天 别忘了电子骨灰盒:24日停止

邓超王二妮春晚登台演唱!导演组:“一稳一疯”

全球视讯!小米汽车机密信息被曝光 设计神似特斯拉Model 3

焦点速读:夏普推出了NEC P627UL激光投影机:亮度高达6200ANSI流明

学习笔记——SSM整合(思路、步骤)

《流浪地球2》看不懂?专业科普来了 刷完电影来看看

焦点滚动:美国海关拆坏任天堂游戏稀有原封卡带:价值离谱

每年在中国收入500亿:连苹果都惹不起它

环球要闻:牌面!曙光新型计算机亮相《流浪地球2》

全球热点评!高端顶级大屏Win掌机!AYANEO KUN官宣:中文名叫“鲲”

世界信息:女子网购短裤7个月后异地签收 包裹跑遍广州、北京全国多地

【世界热闻】老外愤怒!2000块的旗舰SSD 990PRO 写了2T寿命暴跌至95%:竟遭三星拒保

焦点消息!适配器模式

环球百事通!《流浪地球2》上映首日吸金4.4亿!吴京主演作品票房突破290亿元

世界报道:男子包饺子放金戒指被网友质疑 霸气回应称自家开金店、寓意长寿多福

吃年夜饭鱼刺卡喉 医生一晚接诊近40例 提醒:切勿自行处理

沈腾可能要请很多人吃饭了!讲述小品《坑》背后:临场改词

山东一大妈首次放加特林烟花犹如上战场:网友评价“入戏太深”

学习笔记——SpringMVC拦截器的两种装配方式;SpringMVC拦截器工作原理;SpringMVC中的异常处理器;SpringMVC工作原理

【环球新要闻】俄宇航员从太空拍到除夕夜的中国:灯火通明、烟火璀璨

热推荐:雷军拍小米贺年照害羞了 现场即兴幽默:祝愿“暴富”会不会价值观有问题?

亚马逊、微软、谷歌之后:消息称苹果已经开始裁员

【天天新要闻】OPPO Find X6标准版屏幕素质拉满:支持2160Hz高频PWM调光

当前观察:网飞美剧《三体》杀青:美女云集!网友直呼汪淼演员毁三观

环球百事通!读函数式编程思维笔记03_权责让渡

科技改变生活!男子为“吃福币”用上金属探测器

性能太炸!AMD“热那亚”EPYC 9654成PassMark最快CPU

2.7公斤带剧毒!澳大利亚发现巨型海蟾蜍:已被安乐死

【天天新视野】maven的安装和配置

董宇辉回村放烟花 衣服烧了几个洞 网友:过年开心就好

总导演透露春晚因为沈腾启动了预案:不是因麦掉了 小品演短两分多

B. Emordnilap【Codeforces Round #845 (Div. 2) and ByteRace 2023】

张若昀成春晚吃烧鸡第一人 华强北连夜赶工上架同款手机壳

世界速看:AI当街罢工 通用无人驾驶出租车路上趴窝:致拥堵20分钟

报道:iPhone 15系列外形焕然一新!弧形边框回归:屏幕黑边窄得创纪录

快消息!中期改款宝马X5即将亮相

男子赶集花300元买五彩大公鸡:专业养殖户都没见过

天天速递!兔年大年初一电影票房破七亿元 《流浪地球2》第一

动态:重的石头也能打出好水漂:研究应用价值竟跟飞机有关!

金靖小品再现最快语速 背出电脑配置:酷睿i9+RTX 4090 Ti春晚“首发”

撒贝宁戴兔头帽回应鞋跟高:画面让人笑翻

环球观点:2023年春节档唯一科幻大片!吴京主演《流浪地球2》今日上映

环球实时:学习笔记——拦截器与过滤器的区别;拦截器概述;拦截器中三个方法

天天观速讯丨联想Thinkbook 16p公布:酷睿i9+RTX 4060 还支持磁吸配件

天天信息:苹果正在开发类似iPad的智能显示器!要进军智能家居

当前看点!笔记本外接显卡坞实测:RTX 4090损失20%性能 等同RTX 4080水准

全球今热点:支付宝五福开奖!你分到了多少?

Ubuntu 终端美化(oh-my-zsh)

技嘉AORUS Gen4 7300 SSD换上新闪存:顺序速度提升明显 飙到7.3GB/s

全球热点!七彩虹上架新款RTX 3050显卡:降低功耗、1999元

天天热文:2023年春晚今晚呈现:霸榜微博热搜

全球微动态丨非遗南音元素首登春晚:被称为“中国音乐史上的活化石”

《漫威复仇者联盟》即将停运 玩家:微交易毁了游戏

环球快资讯丨丰盛!神舟十五号乘组太空年夜饭菜单出炉:有熏鱼、水饺等19样

环球即时:Wallpaper壁纸提取得到tex文件,tex文件转图像,tex文件转png,tex文件提取壁纸,Wallpaper壁纸提取无法得到图像文件,ReP

环球新动态:学习笔记——SpringMVC文件上传与下载

五彩斑斓的烟花到底是化学反应还是物理反应?

Ubuntu22.04 安装 ssh

快看:西北唯一!西安全城红绿灯倒计时上线百度地图:支持语音提醒