最新要闻

- Meta宣布开源大规模语言模型 可应对多达4000种以上音声语言识别

- 每日速讯:JDG夺冠故事公开,Ruler曾想过退役,被GEN放弃后,真的很难受

- 腾讯电竞发文正式官宣亚运征途 共29支国家及地区代表队参与

- 乐高公开与《吃豆人》的联动积木 将于6月1日正式上市

- 首发2599元 联想小新台式机上架:12代10核U、1TB大存储-环球新消息

- 浙江震元:5月12日召开业绩说明会,投资者参与|世界看热讯

- 《信访工作条例》你了解吗?“十问十答”来挑战! 全球快报

- 天玑9200+安卓王者 iQOO Neo8 Pro淘汰12G内存:起步就是顶配

- iQOO Neo8 Pro亮相:全球首发天玑9200+ 跑分屠榜安卓阵营 全球资讯

- 你用过么?闲鱼宣布用户数已突破5亿 新要闻

- 微速讯:行业首发!iQOO Neo8系列搭载穿墙天线簇技术:下载提速30%

- 当前消息!还能撑多久?威马汽车被强制执行超一千万元

- 资讯推荐:《三国志·战略版》侵权《率土之滨》被判赔网易5000万 !不服要上诉

- 一线经销商们的销售话术 真是把竞品往死里整啊

- 曝宝马1系停产并取消 X2不再国产!网友:宝马梦没了

- 旅泰大熊猫“林惠”死因调查结果出炉:多器官功能衰竭

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

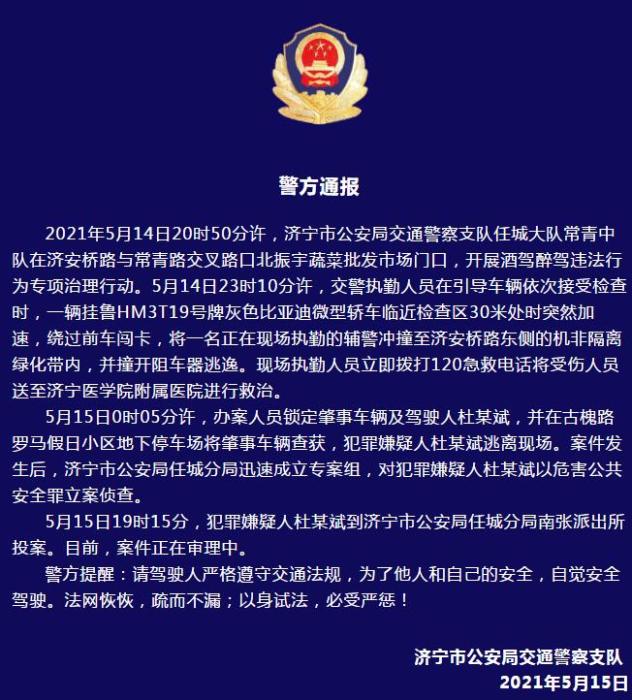

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

世界短讯!08-避免Latch的产生

(资料图片)

(资料图片)

1.Latch简介

Latch就是锁存器,是一种在异步电路系统中,对输入信号电平敏感的单元,用来存储信息锁存器在数据未锁存时,输出端的信号随输入信号变化,就像信号通过一个缓冲器,一旦锁存信号有效,数据就会被锁存,输入信号不起作用,因此,锁存器也被称为透明锁存器,指的是不锁存时输出对于输入是透明的

2. 异步电路与同步电路

异步电路:异步电路主要是组合逻辑,用于产生FIFO或者RAM的读写控制信号脉冲,但是它同时也用在时序电路中,此时它没有统一的时钟,状态变化的时刻是不稳定的,通常输入信号只在电路处于稳定状态时才发生变化同步电路:同步电路是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有操作都是在严格的时钟控制下完成的,这些时序电路共享一个时钟CLK,而所有的状态变化都是在时钟上升沿(或者下降沿)完成的异步电路中广泛使用的是Latch,在异步电路中可以使用Latch替代寄存器,但是在同步电路中,Latch对于电路会出现不好的结果

- 对于毛刺敏感

- 不能异步复位,上电之后处于不定态

- 占用更多的逻辑资源

- 额外延迟

- 复杂的静态时序分析

3.几种产生Latch的情况及避免

- 组合逻辑中if-else语句,缺少else语句

- 组合逻辑中case条件分支语句条件未完全列举,且缺少default语句(在使用case语句的时候要么完全列举所有情况,要么加default)

- 组合逻辑中输出变量赋值给了自己

4.验证Latch

使用之前写过的3-8译码器进行验证Latch.qpf结尾的文件就是之前创建的quartus项目文件,双击可以打开quartus项目

4.1 正确的代码

module decoder( input wire in_1, input wire in_2, input wire in_3, output reg [7:0] out); always@(*) begin if({in_1,in_2,in_3} == 3"b000) out <= 8"b0000_0001; else if ({in_1,in_2,in_3} == 3"b001) out <= 8"b0000_0010; else if ({in_1,in_2,in_3} == 3"b010) out <= 8"b0000_0100; else if ({in_1,in_2,in_3} == 3"b011) out <= 8"b0000_1000; else if ({in_1,in_2,in_3} == 3"b100) out <= 8"b0001_0000; else if ({in_1,in_2,in_3} == 3"b101) out <= 8"b0010_0000; else if ({in_1,in_2,in_3} == 3"b110) out <= 8"b0100_0000; else if ({in_1,in_2,in_3} == 3"b111) out <= 8"b1000_0000; else out <= 8"b0000_0001; endendmodule4.2 if-else 产生latch

module decoder( input wire in_1, input wire in_2, input wire in_3, output reg [7:0] out); always@(*) begin if({in_1,in_2,in_3} == 3"b000) out <= 8"b0000_0001; else if ({in_1,in_2,in_3} == 3"b001) out <= 8"b0000_0010; else if ({in_1,in_2,in_3} == 3"b010) out <= 8"b0000_0100; else if ({in_1,in_2,in_3} == 3"b011) out <= 8"b0000_1000; else if ({in_1,in_2,in_3} == 3"b100) out <= 8"b0001_0000; else if ({in_1,in_2,in_3} == 3"b101) out <= 8"b0010_0000; else if ({in_1,in_2,in_3} == 3"b110) out <= 8"b0100_0000; else if ({in_1,in_2,in_3} == 3"b111) out <= 8"b1000_0000; // else // out <= 8"b0000_0001; endendmodule4.3 case语句产生latch情况

```plaintextmodule decoder( input wire in_1, input wire in_2, input wire in_3, output reg [8:0] out); // 使用case语句 // 使用if-else语句 always@(*) begin case({in_1,in_2,in_3}) 3"b000 : out = 8"b0000_0001; 3"b001 : out = 8"b0000_0010; 3"b010 : out = 8"b0000_0100; 3"b011 : out = 8"b0000_1000; 3"b100 : out = 8"b0001_0000; 3"b101 : out = 8"b0010_0000; 3"b110 : out = 8"b0100_0000; // 3"b111 : out = 8"b1000_0000; // default : out = 8"b0000_0001; endcase endendmodule正常代码综合

错误代码综合

4.4 将变量赋值给自己

module decoder( input wire in_1, input wire in_2, input wire in_3, output reg [8:0] out); // 使用case语句 // 使用if-else语句 always@(*) begin case({in_1,in_2,in_3}) 3"b000 : out = 8"b0000_0001; 3"b001 : out = 8"b0000_0010; 3"b010 : out = 8"b0000_0100; 3"b011 : out = 8"b0000_1000; 3"b100 : out = 8"b0001_0000; 3"b101 : out = 8"b0010_0000; 3"b110 : out = 8"b0100_0000; 3"b111 : out = 8"b1000_0000; default : out = out; // 将输出变量赋值给自己,也会产生latch endcase endendmodule- 代码每次修改之后都要进行重新编译

关键词:

-

-

-

-

世界短讯!08-避免Latch的产生

3)选课系统

移动政务服务提升突破口——小程序技术-天天新消息

Meta宣布开源大规模语言模型 可应对多达4000种以上音声语言识别

每日速讯:JDG夺冠故事公开,Ruler曾想过退役,被GEN放弃后,真的很难受

腾讯电竞发文正式官宣亚运征途 共29支国家及地区代表队参与

乐高公开与《吃豆人》的联动积木 将于6月1日正式上市

世界即时看!债务违约警告在耳 “白宫三谈”未破僵局

首发2599元 联想小新台式机上架:12代10核U、1TB大存储-环球新消息

浙江震元:5月12日召开业绩说明会,投资者参与|世界看热讯

2)MySQL表管理之创建删除、约束实施、自增长字段、复制表结构

融合地理信息与智能技术:GIS引领智慧城市的发展潮流_天天热资讯

中金湖北科投光谷REIT将于5月29日询价

《信访工作条例》你了解吗?“十问十答”来挑战! 全球快报

天玑9200+安卓王者 iQOO Neo8 Pro淘汰12G内存:起步就是顶配

iQOO Neo8 Pro亮相:全球首发天玑9200+ 跑分屠榜安卓阵营 全球资讯

你用过么?闲鱼宣布用户数已突破5亿 新要闻

微速讯:行业首发!iQOO Neo8系列搭载穿墙天线簇技术:下载提速30%

当前消息!还能撑多久?威马汽车被强制执行超一千万元

记录--使用率比较低的10个Web API_世界新消息

资讯推荐:《三国志·战略版》侵权《率土之滨》被判赔网易5000万 !不服要上诉

一线经销商们的销售话术 真是把竞品往死里整啊

曝宝马1系停产并取消 X2不再国产!网友:宝马梦没了

旅泰大熊猫“林惠”死因调查结果出炉:多器官功能衰竭

天天观速讯丨2K直屏+120W快充!Redmi K60 Pro宣布降价:2699元起

世界快看:贷款一天200的违约金是多少

PTA1~3次作业总结_lxh

百事通!MetaMask 钱包使用 - Solidity开发教程连载

世界热消息:我的第一个项目(十三) :组件间传值的一些方案(vuex,eventbus,localStorage)

每日资讯:商品日报(5月23日):尿素跌超4%领跌商品市场 菜粕创近三个月新高

目前负债1000万的都进来大家都是因为什么_现在生活状态如何|环球即时

焦点速递!阿里云被曝裁员:整体优化比例约7%

天天热资讯!Win11 2024新预览版25370发布:性能提升更好用了

一加和友商都在搞“旗舰普及” 有何区别?李杰回应 世界观天下

世界快资讯:领先AMD!Intel FPGA首发支持PCIe 5.0和CXL 2.0:性能、带宽大幅提升

月销量将再创纪录!理想5月第三周狂卖0.71万辆:真遥遥领先

RocketMQ 在小米的多场景灾备实践案例 每日消息

Algorithm_01--C#递归算法

一兆韦德:经营受疫情影响 已完成新一轮融资

今日关注:5.8元/月 WPS新版超级会员618大促预售:升不升会员简直两个软件

硅谷富豪为长寿拿儿子当血童:换血“永葆青春” 每日快报

任天堂“最失败”主机!官方宣布Wii U维修服务即将终止

特斯拉Model Y路边起火完全烧毁 保险公司赔付一台新车

150W快充!真我GT Neo5 16GB+1TB新版发布:3099元_前沿热点

世界热头条丨国元证券研究所组织开展科技主题基金经理调研

环球热议:海兴电力: 截至目前,公司在海外市场已布局6大生产基地

馅料大于75% 三只松鼠黄金肉松饼7.9元/斤新低

看热讯:《王者荣耀》新英雄曝光:蓝发美人鱼

小米自拍之王来了!产品经理晒自拍对比照:差距高下立判|当前观点

女儿膝下有硬盘 膝盖绑150根SSD走私 因步态有异被查获-当前关注

中国拿下76%造船份额 韩国三大船企之一的大宇退出历史舞台

gps北斗卫星同步时钟(子母钟系统)助力莘莘学子高考精准计时_环球观天下

世界速讯:Ubuntu 18.04 (Bionic) 简单快速的安装mongodb

原生js如何请求接口 今日报

数字转换_全球播报

震惊!二狗子的火锅店被隔壁老王 DDoS 攻击了

杭州热电再度触及涨停|焦点速递

次旗舰RTX 4080移动版独显性能如何?实测揭晓答案_世界快报

比iPhone 14更薄!网友评价小米Civi 3:外观太牛了 工业设计之巅

当前要闻:和AI网聊10分钟被骗430万惊呆全网 官方:AI诈骗成功率接近100%

海拔8300米!我国科研人员成功维护升级世界最高自动气象站:已传回数据_环球观速讯

强电与弱电的区别,你了解吗?

易基因:全基因组DNA甲基化分析揭示DNMT1在斑马鱼模型听觉系统发育中的作用 | 胚胎发育|今日播报

聊聊ElasticeSearch并发写的乐观锁机制 天天快讯

世界热点评!臭名昭著的“Hello,World!”

全球今日讯!没听妈妈话学了物理他拿了诺奖 丁肇中:坚持自己的兴趣和理想

【天天新视野】Intel超级APU:黄了!

越南打工人不加班 一天只干5小时:逼急中国老板 傻子一样

世界微动态丨广州高温费发放标准2023 广州高温补贴几月开始发放?

人工智能将如何改变敏捷项目管理?|当前最新

2步轻松实现ASP.NET Core托管服务执行定时任务_天天资讯

互联网从业人员的知识图谱-天天观速讯

高空坠物致人死亡 36名住户赔偿!专家称非常危险:一定要避免

浙江一公司上4休3收到上千份简历:目前仅有三名员工、盈利只够工资 全球热闻

刀片电池走向全球 多国力邀比亚迪建厂!官方回应

《小美人鱼》IGN 7分:不完全成功 海洋生物太丑!

就在地球上 科学家培育出一个“黑洞”:结果有了惊人发现 环球观天下

环球讯息:你会相信人工智能医生吗

carplay放歌没声音怎么回事_当前头条

MSE 自治服务帮你快速定位解决 Dubbo 重复订阅导致 RPC 服务注册失败问题

springcloud~gateway网关

[css]总结-如何实现水平垂直都居中对齐?

闫衍:经济复苏由结构分化走向全面修复 全年经济增速有望达到5.7%

全球快播:登陆iOS后:安卓版ChatGPT即将上线

家长投诉网红店打卡博主穿着暴露 离学校近影响孩子心理:网友吵翻-热文

世界热讯:华为完成14nm以上EDA替代 更强的国产EDA来了:部分已支持5nm

魅族618开启!魅族20限时直降200元:2999元起 3年超长质保_世界要闻

自拍神器!小米Civi 3前置双主摄:32MP美人镜+32MP超广角|世界速看料

新动态:我国深海装备技术水平持续提升 为南海沉船遗址考古研究提供科技支撑

今日播报!数据驱动的军港革新:智慧可视化助力军事决策

子母钟系统(网络时钟系统)助力高考精准计时工作建设

天天微速讯:云计算遇上电动车,跑出新模式的数智化转型

天天观察:能力惊人!GPT-4通过注册会计师和内审师考试

“小而美”国民爆款车!五菱宝骏悦也售价曝光:或8.38万元起 当前播报

比亚迪研发公司更名方程豹汽车销售公司:王传福卸任董事长

环球观天下!5倍于ChaGPT Intel推出Aurora genAI大模型:1万亿参数

微信5个“隐藏”超强功能 你知道几个? 新资讯

怎么验证苹果手机是不是正品

css 中class包含某元素的选择器-速读

JS中的undefined 与 null_天天热门