最新要闻

- 全球今日报丨女子帮摔倒老人反被指认为肇事者:本人正能量回应获网友点赞

- 今年夏天逃不掉高温了:全球平均气温正在波动上升 全球今头条

- 今亮点!员工回怼加班遭光速开除!公司回应:矛盾来源并不是加不加班

- 环球热门:跟苹果不一样!说到生产力 华为才是真正懂中国人的

- 全球今日讯!《猫和老鼠》才是永远的神!凭什么能碾压AI作画?

- 冲击欧联冠军!穆里尼奥第六次进入欧战决赛,前五次全胜

- 全球今头条!盂县气象局发布雷暴大风蓝色预警【Ⅳ级/一般】【2023-05-19】

- 天天热消息:人寿学平险保障范围_人寿学平险报销范围

- 斗鱼第一季度总净营收为14.831亿元 同期相比下滑17.4%

- 《王者荣耀》游戏官方推出女装品牌 限量的五款连衣裙均未售罄

- 美国蒙大拿州签署法案封禁TikTok 将于2024年1月份执行

- Xbox或将推出全新商业模式 提供游戏片段试玩或带广告的免费游玩

- 因原材料与运输成本上涨 可口可乐或将上演“涨价大戏”

- 我国科研人员成功研制量子计算超低温温度传感器 支持实时温度监测

- 因存在影响游戏竞技公平的缺陷 英雄联盟官方公布部分英雄禁用公告

- 谷歌将加入全新AI生成代码功能 由“文生代码”模型Codey提供支持

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

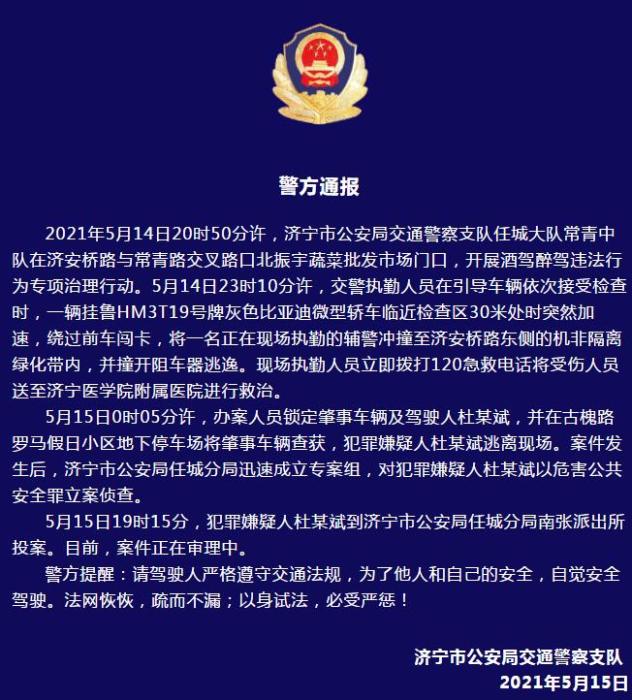

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

全球快看:01-module/分频器/激励写法

【资料图】

【资料图】

1.module

- module有出入接口,输出接口

- module有时钟和复位

// input clock;rest_n; // n表示低电平复位//outputo_data;module module_a( // module是关键字表示声明一个模块 // module module名 // module .. endmodule是一对 // module module_name(模块的输入输出列表); // 输入只能是wire变量,只有线才能连入module // 输出可以是wire类型也可以是reg类型,一般是reg变量 // 不写位宽,默认是1bit位宽的 input wire clk, input wire rest_n, output reg [7:0] o_data // 8bit数据);endmodulemodule Lut_m(input wire sclk,input wire rst_n,input wire [9:0] i_data,input wire [15:0] i_sin,output reg [15:0] o_cos,output reg o_div_clk,output reg [9:0] div_clk, // module中包含子module // 嵌套子模块,就是例化,首先要先将子模块写成单独的模块 // 例化:先写模块的名字 例化的名字 sub_m u_sub_m ( // 如何引入接口 //用点的方式先写模块的接口(接入的接口) .sclk (sclk), .rst_n (rst_n), .i_data (i_data), .i_sin (i_sin), .o_cos (o_cos), .o_data (o_data) ); sub_n u_sub_n( .sclk (sclk), .rst_n (rst_n), .i_data (i_data), .i_sin (i_sin), .o_data (o_data) ););endmodule2.分频器

// 输入50MHz,二分频module div_clk( input wire sclk, input wire rst_n, output reg div_clk_o); // 分频器,需要一个计数器,二分频,需要记录01状态,1bit // div_cnt就是一个计数器 // 计数器为0的时候,输出为低,计数器为1的时候,输出为高 reg div_cnt; //寄存器使用always语句进行赋值的 // 这是一种异步复位的写法 // 在时钟上升沿的时候触发逻辑 // 复位使用作用下实现复位逻辑 // 计数器逻辑 always@(posedge sclk or negedge rst_n) begin if(rst_n == 1"b0) begin div_cnt <= 1"b0; end else begin div_cnt <= div_cnt + 1"b0; end end // 产生div_sclk_o always@(posedge sclk or negedge rst_n) begin if(rst == 1"b0) begin div_cnt <= 1"b0; end else if(div_cnt == 0) begin div_clk_o <= 1; end else div_clk_o <= 0; endendmodule- div_cnt = 0的时候,给输出赋值1,下一个时钟上升沿就可以输出1

- div_cnt = 1的时候,给输出赋值0,下一个时钟上升沿就可以输出0在时序电路里,一般系统时钟都是高频的,不同外设对时钟频率的要求不同,所以需要通过分频来获得相应的时钟频率,一般都是将高频的时钟转换为低频的时钟。最简单的分频就是2分频,也就是把时钟频率减半,输出时钟和输入时钟上升沿对齐,波形图是这样的:有遇到需要奇数分频的时候,这时候上升沿和下降沿都需要用到,3分频波形图是这样的:上面两张图都是50%占空比的,有的时候我们只需要用输出时钟的上升沿,不需要考虑下降沿,这样的话我们的输出时钟只需要是单脉冲的就可以了,设计的时候会简单很多,单脉冲的3分频波形图是这样的:

8分频 -- 4周期反转一次4分频 -- 2周期反转一次3分频 -- 1.5周期/3周期5分频 -- 2.5周期/5周期7分频 -- 3.5周期/7周期后期会补充分频器和计数器的书写方式

关键词:

-

全球快看:01-module/分频器/激励写法

1 modulemodule有出入接口,输出接口module有时钟和复位 inputclock;rest_n; n表示低电平复位 outputo_da

来源: -

-

-

全球快看:01-module/分频器/激励写法

全球动态:DDR2 学习笔记(一)

全球今日报丨女子帮摔倒老人反被指认为肇事者:本人正能量回应获网友点赞

今年夏天逃不掉高温了:全球平均气温正在波动上升 全球今头条

今亮点!员工回怼加班遭光速开除!公司回应:矛盾来源并不是加不加班

环球热门:跟苹果不一样!说到生产力 华为才是真正懂中国人的

全球今日讯!《猫和老鼠》才是永远的神!凭什么能碾压AI作画?

冲击欧联冠军!穆里尼奥第六次进入欧战决赛,前五次全胜

全球今头条!盂县气象局发布雷暴大风蓝色预警【Ⅳ级/一般】【2023-05-19】

天天热消息:人寿学平险保障范围_人寿学平险报销范围

斗鱼第一季度总净营收为14.831亿元 同期相比下滑17.4%

《王者荣耀》游戏官方推出女装品牌 限量的五款连衣裙均未售罄

美国蒙大拿州签署法案封禁TikTok 将于2024年1月份执行

Xbox或将推出全新商业模式 提供游戏片段试玩或带广告的免费游玩

因原材料与运输成本上涨 可口可乐或将上演“涨价大戏”

我国科研人员成功研制量子计算超低温温度传感器 支持实时温度监测

因存在影响游戏竞技公平的缺陷 英雄联盟官方公布部分英雄禁用公告

谷歌将加入全新AI生成代码功能 由“文生代码”模型Codey提供支持

谷歌将联合东京大学与芝加哥大学共同研究量子计算机 预计投入超千万资金

世界首例泰坦尼克号3D全景扫描图像完成 只为探索沉船新发现

Knight突然开团,对位Faker出杀人书,JDG完美表现,28分钟击溃T1 天天热推荐

当前信息:下个月你工资卡里或将多一笔钱!领取高温津贴

号称保值的iPhone手机今年疯狂掉价!花5000多还不如买安卓|世界热点

Springboot集成Netty实现TCP通讯_天天速看料

【聚看点】誉的拼音和组词怎么写_誉的拼音

698元!华为儿童手表5发布:无网离线也能定位

数毛社Steam Deck测评:新三A大作性能表现开始吃紧

一次装修十年无忧!华为全屋智能4.0发布:业界首款空间穿越屏|全球热消息

每日聚焦:4K旗舰领衔!Vidda连发三款投影仪:画质、亮度直接拉满 3199元起

81岁老妪拒绝医美|今日报

海通恒信(01905):“21恒信G2”回售登记期为5月23日至25日

【世界独家】阿里巴巴核心业务:云智能部门将成为独立上市公司

热点!车企们 请别拿人命开玩笑

华为十大新品价格汇总:MateBook X Pro笔记本顶配1.4万元-天天即时

三大专业升级 华为MateBook 16s 2023来了:重度生产力标杆之作

业界首款支持高血糖!华为WATCH 4 Pro蔚蓝地球图赏 当前快看

全球热文:win7屏幕保护设置在哪里 win7屏幕保护设置

ET介绍——强大的基于.dotnet7+Unity3d的双端C#开源游戏框架-全球报资讯

热推荐:Java设计模式-外观模式

python包管理工具:Conda和pip比较

债市日报:5月18日

每日快讯!凯华推出“黑莓冰淇淋”轴体:加长轴心敲击更清脆

全球速读:北斗导航年产值超5000亿元!12nm芯片重大突破

摩托“骑士”双手离把耍酷还发抖音炫技 被“顺网线”找到_今亮点

安卓用户正在加速逃离:为何买苹果手机的人越来越多了?

1499元起 努比亚N5发布:6nm国产芯 今日报

煜邦电力: 关于回复上海证券交易所《关于北京煜邦电力技术股份有限公司向不特定对象发行可转换公司债券的审核中心意见落实函》的公告

热文:【一步步开发AI运动小程序】一、准备工作

python标准模块介绍 -Base64: Base64, Base85等数据编码|全球时讯

学系统集成项目管理工程师(中项)系列22b_信息化知识(中)

express框架的基本使用 环球新资讯

幺妹带你慢慢耍歌词完整版_请问老师们有谁知道幺妹带你慢慢耍歌词曲谱 这首歌确实不错好听

拒绝录用有文身员工 老板回应被威胁:看不惯年轻人必教育到底

滚动:《塞尔达传说:王国之泪》掉帧严重:任天堂Switch性能不够用了

排面!理想L7成卢森堡大使馆官方用车:“这是中国最棒的车”_关注

环球今日讯!预制半成品、来“料”加工、网上销售 普陀警方捣毁一伪造、买卖身份证件黑色产业链

论文、专利、文献检索及图像数据工具总结 时讯

工控老曹说——TSN标准化如何赋能多领域以太网新发展

焦点讯息:2023最佳python编辑器和IDE

git 常用指令-当前聚焦

今日精选:万家基金尹诚庸离任6只基金

iQOO首款降噪无线耳机来了:将与Neo8系列同步推出

悲惨的5G基站:你敢建?我就敢拆!

害怕失去灵魂?大众汽车:我们没使用华为车机软件|环球快讯

焦点热议:小黑旗舰升级13代酷睿!联想2023款ThinkPad X1 Carbon国内发布

世界快看点丨马斯克再度催生:再不生娃人类就要灭亡了

苏联题材科幻动作游戏《原子之心》Steam 史低促销

微服务圣经1:零基础搭建一套SpringCloud微服务脚手架(SpringCloud+Dubbo+Docker+Jenkins) 环球速递

低代码开发——进最热的赛道,啃最硬的骨头-视焦点讯

Python字符串替换的3种方法-播资讯

Django SQL注入漏洞复现 (CVE-2022-28347)

每日机构分析:5月18日

天天热资讯!斗罗大陆:为何唐三成为海神后,只赠予了吉祥一个神赐魂环,

我国本月将发射神舟十六号载人飞船:与神舟十五号乘组在轨交接-消息

【世界速看料】充电时 先插手机还是充电器?这几种方法都错了

正面挑战微软!谷歌宣布将推出AI写代码功能

来了!消息称RTX 4060 Ti今晚发布:NV定8/16GB版价格 或399美元

环球今头条!小米13旗舰主摄下放!小米Civi 3关键参数曝光:IMX800加持

陈张开展“进企业促发展”人大代表履职建功主题活动 焦点精选

九头蛇的安装与使用 世界热议

焦点热门:第二章:数据模型与查询语言

P1344 [USACO4.4] 追查坏牛奶 Pollutant Control (网络流)

MySQL 迁移至 SQLite 问题记录 全球通讯

全球今日报丨【新华500】新华500指数(989001)18日下跌0.14%

当前时讯:最高检发新文:NFT法律属性定调哪般?

天天日报丨黄桃+椰果!林家铺子双色水果罐头8罐仅19.9元

天天头条:比亚迪再掀桌子!新款汉DM-i冠军版上市:18.98万起合资还怎么玩

同事都说买高像素就对了 四款热门高像素全画幅相机推荐-天天百事通

微资讯!HTC U23 Pro发布:性价比这么低的手机不多了

世界热点评!日赚4亿还嫌多?移动联通电信现在和10年前日赚一样多:手机资费下降95%等

百度投资卡车整车研发商载合汽车科技_环球快讯

环球热点![MySQL 如何分析性能]

天天速递!Python从零到壹丨图像增强的顶帽运算和底帽运算

知识拷问:工作站和服务器哪个更适合做CST电磁仿真?|每日观察

今日讯!3万多买钻戒如今只值2000元 网友称还是黄金保值:你会买钻戒吗?

60Hz显示器配120帧显卡是浪费?答案意外_世界即时看

最新资讯:包含多家中国造车新势力!马斯克预言一年内必有车厂倒闭

360 AIGC产品定名360智脑、360鸿图

三星量产12nm DDR5内存:功耗骤降23% 全球新视野

追讨欠款的有效期限是多久?欠钱不还电话不接微信不回怎么办?