最新要闻

- 配双激光雷达!传新款小鹏P7定名小鹏P7i 3月上市

- 世界快看:租客跟房东说养宠物结果是匹马 发现时房间堪比垃圾场

- 当前观点:北京一地铁口现煎饼果子机器人:3分钟一个 可选要不要香菜

- 世界热点!全国第一!广西率先实现双千兆网络覆盖所有行政村

- 天天视讯!微软技术测试“玩出”新花样:实现《我的世界》AI自动建造

- 【环球快播报】公园飞无人机 被男子一板凳拍在地上:怕伤到孩子

- 环球新消息丨为1个亿目标 26岁“背景太假哥”拼了:每天冒严寒、酷暑直播

- 全球看点:智慧管理+贴心服务,这座网红公厕不“简单”

- RTX 4070笔记本挤牙膏?只比RTX 3070快了11%

- 天天热资讯!史上第25个!浙江彩民69元中2.4亿元巨奖 网友调侃:又骗我买彩票

- 全球热讯:不能“回血”了!微软大作《红霞岛》实体版仅提供激活码

- 0反式脂肪酸!旺旺邦德轻乳咖啡官方清仓:9瓶1盒仅19.9元

- 目标基辅号

- 环球观点:鹡鸰女神第2集-鹡鸰女神无修版

- 环球新动态:雷军宣布小米参加MWC 2023大会!铁大、铁蛋机器人海外亮相

- 上海一特斯拉再现失控事故:成道路护栏“终结者”

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

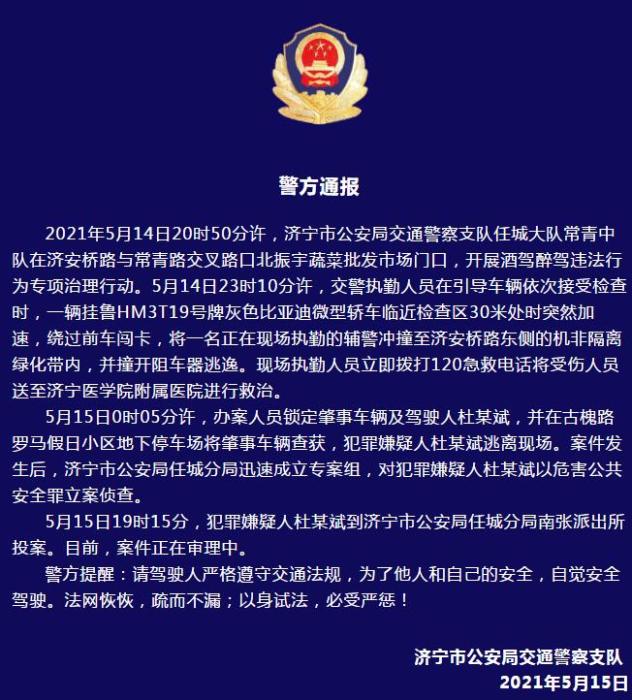

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

世界简讯:FPGA基于ACM2108的DDS设计

(资料图)

(资料图)

这次设计一个DDS信号发生器。该设计的特点有:

- 双通道的DA输出,可以调节频率、相位、和波形(正弦波、方波、三角波)。

- 拥有相位重置的功能,能够同时重置两个输出波形的相位。本次采用的是小梅哥的ACM2108模块。该模块有两个通道的ADC和两个通道的DAC。本次设计的前置是DDS基本模块,具体可点击链接查看。DDS基本模块在加入了装有正弦波数据的ROM的基础上,再添加三角波和方波的数据的ROM,从而能够切换输出的波形。通过调用VIO这个IP核,设置输出信号的频率、相位和波形。然后通过LIA这个IP核,去观察数据波形。

一、模块代码

`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company: GDUT// Engineer: Lclone// // Create Date: 2023/02/02 22:34:21// Design Name: DDS_ACM2108// Module Name: DDS_ACM2108// Project Name: DDS_ACM2108// Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision:// Revision 0.01 - File Created// Additional Comments:// //////////////////////////////////////////////////////////////////////////////////module DDS_ACM2108( input Clk, input Rst_n, output DA_Clk_ch1, output [7:0] DA_data_ch1, output DA_Clk_ch2, output [7:0] DA_data_ch2, output AD_Clk_ch1, input [7:0] AD_data_ch1, output AD_Clk_ch2, input [7:0] AD_data_ch2 ); wire Clk_125M; wire [31:0] Fword_ch1; wire [11:0] Pword_ch1; wire [ 1:0] mode_sel_ch1; wire [31:0] Fword_ch2; wire [11:0] Pword_ch2; wire [ 1:0] mode_sel_ch2; reg [7:0] AD_data_ch1_reg; reg [7:0] AD_data_ch2_reg; wire Wave_rst_p; always@(posedge Clk)begin AD_data_ch1_reg <= AD_data_ch1; AD_data_ch2_reg <= AD_data_ch2; end ila_0 ila_0_DA ( .clk(Clk_125M), // input wire clk .probe0(DA_data_ch1), // input wire [7:0] probe0 .probe1(DA_data_ch2) // input wire [7:0] probe1); ila_1 ila_1_AD_ch1 ( .clk(Clk), // input wire clk .probe0(AD_data_ch1) // input wire [7:0] probe0); ila_1 ila_1_AD_ch2 ( .clk(Clk), // input wire clk .probe0(AD_data_ch2) // input wire [7:0] probe0); clk_wiz_0 clk_wiz_0_inst ( // Clock out ports .clk_out1(Clk_125M), // output clk_out1 // Clock in ports .clk_in1(Clk)); // input clk_in1 DDS_Cmd_VIO DDS_Cmd_VIO_inst ( .clk(Clk_125M), // input wire clk .probe_out0(Fword_ch1), // output wire [31 : 0] probe_out0 .probe_out1(Pword_ch1), // output wire [11 : 0] probe_out1 .probe_out2(mode_sel_ch1), // output wire [1 : 0] probe_out2 .probe_out3(Fword_ch2), // output wire [31 : 0] probe_out3 .probe_out4(Pword_ch2), // output wire [11 : 0] probe_out4 .probe_out5(mode_sel_ch2), // output wire [1 : 0] probe_out5 .probe_out6(Wave_rst_p) // output wire [1 : 0] probe_out5 ); DDS_Base DDS_Base_ch1( .Clk (Clk_125M), .Rst_n (Rst_n & ~Wave_rst_p), .Fword (Fword_ch1), .Pword (Pword_ch1), .mode_sel (mode_sel_ch1), .DA_Clk (DA_Clk_ch1), .Signal_data (DA_data_ch1) ); DDS_Base DDS_Base_ch2( .Clk (Clk_125M), .Rst_n (Rst_n & ~Wave_rst_p), .Fword (Fword_ch2), .Pword (Pword_ch2), .mode_sel (mode_sel_ch2), .DA_Clk (DA_Clk_ch2), .Signal_data (DA_data_ch2) ); assign AD_Clk_ch1 = Clk; assign AD_Clk_ch2 = Clk; endmodule二、上板结果

我将ACM2108的ad接口与da接口进行连接,然后通过ila观察AD和DA的波形来观察设计是否成功。在观察方波信号的时候,vivado可能会帮我们的波形做处理,导致我们观察的方波变成三角波,这里我们在Analog Settings里将Interpolation style改为Hold即可设置为正常显示的波形。以下是上板后的结果:程序上板后,可以输出频率和相位可调的正弦波、方波、三角波。

-

-

-

-

世界简讯:FPGA基于ACM2108的DDS设计

配双激光雷达!传新款小鹏P7定名小鹏P7i 3月上市

世界快看:租客跟房东说养宠物结果是匹马 发现时房间堪比垃圾场

当前观点:北京一地铁口现煎饼果子机器人:3分钟一个 可选要不要香菜

ArcGIS Pro SDK 001 基于SDK创建第一个插件

每日精选:linux limits.conf 生效,linux修改limits.conf不生效

[数据结构] 稀疏矩阵的加法与乘法

世界热点!全国第一!广西率先实现双千兆网络覆盖所有行政村

天天视讯!微软技术测试“玩出”新花样:实现《我的世界》AI自动建造

观焦点:Module理解及使用

环球今日报丨【算法训练营day49】LeetCode121. 买卖股票的最佳时机 LeetCode122. 买卖股票的最佳时机II

全球时讯:IDEA如何使用Maven不通过模板创建javaWeb项目

【速看料】golang执行命令 && 实时获取输出结果

【速看料】[Qt开发/毕业设计/求职项目]局域网环境下远程文件发送部署系统-服务端、客户端双端的讲解

【环球快播报】公园飞无人机 被男子一板凳拍在地上:怕伤到孩子

环球新消息丨为1个亿目标 26岁“背景太假哥”拼了:每天冒严寒、酷暑直播

全球看点:智慧管理+贴心服务,这座网红公厕不“简单”

【快播报】[数据结构] 稀疏矩阵的转置与快速转置

天天微动态丨关于Linux升级内核时报错-grub2-editenv: error: environment block too small.

RTX 4070笔记本挤牙膏?只比RTX 3070快了11%

天天热资讯!史上第25个!浙江彩民69元中2.4亿元巨奖 网友调侃:又骗我买彩票

全球热讯:不能“回血”了!微软大作《红霞岛》实体版仅提供激活码

焦点报道:0X01 位运算笔记

P4171 满汉全席

0反式脂肪酸!旺旺邦德轻乳咖啡官方清仓:9瓶1盒仅19.9元

目标基辅号

环球观点:鹡鸰女神第2集-鹡鸰女神无修版

环球新动态:雷军宣布小米参加MWC 2023大会!铁大、铁蛋机器人海外亮相

【世界快播报】(数据库系统概论|王珊)第五章数据库完整性-第四、六、七节:约束命名子句、断言和触发器

上海一特斯拉再现失控事故:成道路护栏“终结者”

全球实时:插混和增程路线谁更好?院士欧阳明高给出答案

上海中环内圈发生单车事故 官方通报:车辆起火翻滚地面 驾驶员死亡

每日速讯:F - 树状数组 2【GDUT_22级寒假训练专题五】

全球新资讯:ChatGPT大火 马斯克批OpenAI违背初心:被微软控制 只顾赚钱

贵南高铁全线静态验收:时速350公里 南宁到贵阳时间缩短一半

速看:05-python运算符

【全球聚看点】字节二面:10Wqps超高流量系统,如何设计?

全球快看:动态规划解决最值、有多少方案之类问题

[奶奶看了都会]ChatGPT接入企业微信成为聊天机器人

世界观热点:蹲夜叉还有意外收获?变异蝴蝶直接就往脸上刷啊!

今日热讯:暴雪宣布《暗黑4》新雕像

43年的友情!马云低调现身墨尔本 与昔日好友相见

每日视点!男子将比亚迪海豚改装称房车:车内洗澡、看电影、吃火锅

全球热点!仿豆瓣发布-编辑框自适应高度,自动滚动定位到焦点输入

今日热门!(数据库系统概论|王珊)第五章数据库完整性-第一、二、三节:数据库三大完整性

精选!特斯拉前脸被完全撞烂 气囊没弹!车主:可以去维权吗?

当前聚焦:《地下城与勇士》大面积更改名称、美术素材 玩家喊话中消协:退钱

环球通讯!特斯拉创始人:自动驾驶是胡扯 汽车不应像iPhone

【天天新要闻】AMD、NV把显卡卖到万元 Intel成救星:下代能冲RTX 4080

手机预置软件影响用户体验 央媒揭秘幕后原因:厂商利益驱动

全球视点!苹果上新348元省电保护膜!网友:觉得贵的不是目标客户

读Java实战(第二版)笔记14_CompletableFuture及反应式编程背后的概念

如果我种一个橄榄核,它会长成一棵树吗?

天天即时:全球第10 三星Galaxy S23 Ultra相机DXO等分140:不敌小米11 Ultra

《塞尔达传说:王国之泪》日本最新海报曝光:腐朽大师剑现身

讯息:《生化危机4:重制版》硬件要求出炉:开光追 A卡很受伤

仰望银河背后 吉利是真着急了

散片就是这么来的?男子腰缠155片CPU入境被海关查获

【全球热闻】SpringBoot中统一API返回格式的两种方式

焦点消息!C#两个特殊的集合类StringCollection与StringDictionary

每日聚焦:03-数据类型

快播:期末复习——虚拟内存

速讯:04-数据类型转换

当前报道:安卓机皇!三星Galaxy S23 Ultra下周首销:价格对标iPhone 14 Pro Max

环球热讯:蜜雪冰城门店没关音响扰民一宿 客服:门店整改 向周围居民送冰淇淋致歉

RTX 40系移动平台性能测试出炉:RTX 4080与RTX 4090差距极小

世界新消息丨日本新生儿数量首次跌破80万 创有统计以来最低值:789万老人还在打零工

全球快播:iPhone 14最高降1600元 苹果经销商贴本卖机:谁还买安卓?

九型性格系统_0型血女生的性格

世界快资讯丨首届中国非遗保护年会开幕 四川非遗项目精彩亮相

简讯:超过年限要报废!老人用高压锅炖肉脸部被重伤

女子网购奶粉4个月吃剩半罐退货:被店家吐槽似乞丐

官方称《狂飙》拍摄地拍照收费算勒索: “刀哥”回应不是我 行为不可取

头条焦点:伸展树(Splay)详解

当前简讯:期末复习——内存管理

报道:django连接ubuntu22下的mysql8

打造自己的ChatGPT:逐字打印的流式处理

从矩阵的谱半径到神经网络梯度消失

当前速读:女子厨房接水时速热水龙头突然爆炸冒白烟:爆炸声堪比雷响

【天天时快讯】特斯拉Model 3追尾公交1死1伤 事故已影响销售:网友关心刹车问题

全球快资讯丨女子屋内湿度表1年数值不变 好奇拆下检查后无语:还以为是坏的

世界时讯:【JS】Pug调用自定义JS函数

头条:Java正则匹配域名白名单

曾经很火但消失了的APP!网友第一个想到的是”腾讯微博“

环球即时:女子入住网红酒店发现床垫有尿渍:满房一股味

防AI越界!微软将出手:把必应聊天回复限制在5条以内

天天热文:全球最高安全标准 我国自研华龙一号技术:太平岭核电预计2025年投产发电

天天热资讯!挑战全网最土的“公主下午茶” 让人看饿:网友感慨羞辱多少爱装腔作势人

【新要闻】组合数学_第1章_排列与组合

每日消息!称霸意甲的非洲新一代神锋,奥斯梅恩正在征服足坛

让NV对30系显卡降价不可能!厂商清仓RTX 3080:2年后价格重回首发价

全球观速讯丨《文明6》已玩腻 等了7年的《文明7》官宣:主管大换血

环球关注:tui.editor一款功能强大的markdown编辑器

热消息:关于python中将字典的所有key组成一个列表的方式

【环球报资讯】Cesium CallbackProperty(十五)

【世界独家】全天候显示能掉多少电?iOS 16.4告诉你

环球观速讯丨公司回应要求员工扫厕所:这是福利 每月有几十元奖励

焦点日报:冲击40亿有望!《流浪地球2》累计票房已超38亿

女子情人节翻垃圾桶捡到金链:最后被前主人要回 网友热议

全球速读:【算法训练营day48】LeetCode198. 打家劫舍 LeetCode213. 打家劫舍II LeetCode337. 打家劫舍III