最新要闻

- 变天了!x86 PC陨落:ARM大暴走

- 高通憋出新大招:4G杀手来了

- 国美电器多个破产申请被驳回 苏泊尔在列

- 当前关注:脸都不要了!《黑棉花:悟能》无耻碰瓷《黑神话:悟空》

- Intel中国特供新U i7-13790F开卖:缓存多3MB 竟贵了150元!

- 最资讯丨吴京与粉丝合照被滤镜坑惨:没有明星能逃过美颜摧残

- 环球时讯:明天上映!《流浪地球2》发布港版预告片:MOSS竟然说英文

- 科大讯飞:类ChatGPT技术今年5月落地 AI学习机产品先用

- 天天速看:31.98万元!理想L7 Air发布:性能不变 无空气悬架

- 天天速读:三星S23 Ultra拍月亮100倍变焦的效果:把马斯克都惊艳到了

- 暴雪关停国服后 CEO发声:游戏行业被亚洲主宰 东西方竞争不平衡

- 累计交付27万台 李想:理想成为国内家庭消费者首选豪华SUV

- 世界最新:高通全球首发5G NR-Light基带:主打中端物联网、峰值速率220兆

- 城市行驶每公里仅1毛钱!理想L7出行成本不足宝马X5十分之一

- 宗申新款电动车闪电侠发布:续航超200公里 仪表盘可手机投屏

- 环球观速讯丨丢失两年的手机半夜仍被人试图解锁 被系统远程拍下照片

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

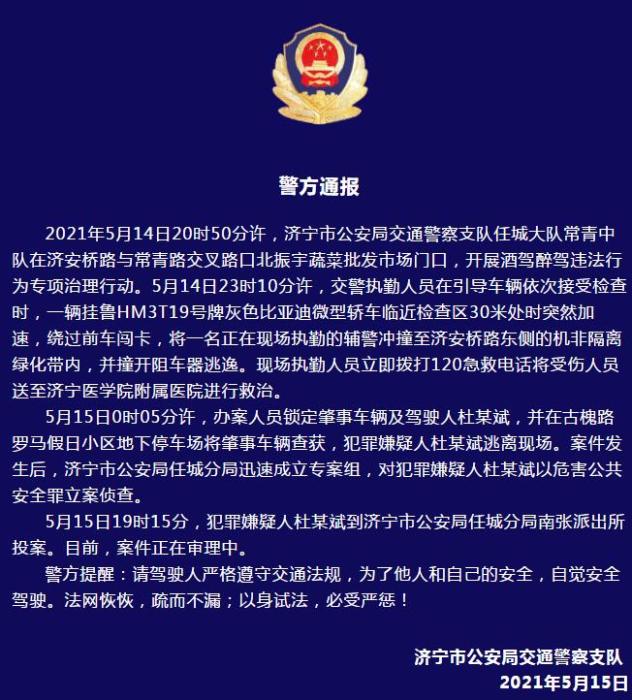

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

高层次综合器(Vivado HLS)的设计流程[原创www.cnblogs.com/helesheng]

最近在写一本Xilinx的FPGA方面的书,现将HLS部分内容在这里分享给大家,希望大家喜欢,也欢迎批评指正。以下原创内容欢迎网友转载,但请注明出处:https://www.cnblogs.com/helesheng

下面用一个简单实例来演示使用高层次综合器进行硬件设计的流程,带领读者以点带面的掌握Vivado HLS的设计方法。

有限冲击响应滤波器,简称FIR(Finite Impulse Response)滤波器,是数字信号处理系统中最常见的算法之一。相比无限冲激响应滤波器(IIR)滤波器而言,FIR滤波器虽然计算效能较低,但它具有以下两个明显优势:

(资料图片仅供参考)

(资料图片仅供参考)

(1)严格线性相位;

(2)冲击响应长度有限,永远稳定。

可编程逻辑器件的高并行性、计算速度快的优势,正好克服了FIR滤波器计算量大的劣势。下面以FIR滤波器的实现为例,介绍HLS的开发和优化流程。实验内容及步骤如下:

1、打开Vivado HLS(Vivado HLS是一个单独的应用程序,可以不依赖于Vivado打开),如图8.2.1所示,单击开始界面的Create New Project。

图8.2.1 新建Vivado HLS工程界面

2、如图8.2.2所示,输入新建的工程名称,指定路径,单击Next。

图8.2.2 在指定目录创建工程

3、在如图8.2.3和8.2.4所示的界面,分别添加已有的设计文件和测试脚本。(初次创建工程,可以不添加任何文件或脚本,单击Next跳过)

图8.2.3 添加已有的设计文件

图8.2.4 添加已有的测试脚本

4、在图8.2.5所示的方案配置界面中,设置默认的时钟周期为10ns,单击Part Select区域右侧的选择按钮,并在弹出的图8.2.6所示界面中筛选工程中使用的器件。返回方案配置界面,单击Finish完成新建工程。

图8.2.5 配置方案界面

图8.2.6 选择工程中使用的器件

5、右键单击工程主界面左侧的Explorer栏的Source,选择New File,新建一个fir.h文件和一个fir.c文件。

头文件内容:

1 #ifndef FIR_H_ 2 #define FIR_H_ 3 #define N 11 4 typedef int coef_t; 5 typedef int data_t; 6 typedef int acc_t; 7 void fir ( 8 data_t *y, 9 coef_t c[N+1],10 data_t x11 );12 #endif代码8.3

C语言源码:

1 #include "fir.h" 2 void fir(data_t *y,data_t x) 3 { 4 coef_t C[N] = { 53,0,-91,0,313,500,313,0,-91,0,53}; 5 data_t shift_reg[N]; 6 acc_t acc; 7 int i; 8 acc=0; 9 Shift_Accum_Loop: 10 for (i=N-1;i>=0;i--) {11 if (i==0) {12 shift_reg[0]=x;13 data = x;14 } 15 else {16 shift_reg[i]=shift_reg[i-1];17 data = shift_reg[i];18 }19 acc+=data*c[i];; 20 }21 *y=acc;22 }代码8.4此时Vivado HLS的界面如图8.2.7所示。

图8.2.7 Vivado HLS工作界面

6、单击上图界面中的Project菜单,选择Project Setting…,在弹出的图8.2.8界面左侧选择Synthesis,并在右侧的Synthesis Setting界面中配置本工程的顶层函数为fir.c文件中的fir函数,随后单击右下角的OK按钮,确认选择。

图8.2.8 配置工程的顶层函数

7、单击工程界面上方的运行C语言综合按钮(图8.2.7所示界面上方的绿色三角形按钮),Vivado HLS将对C语言源文件进行分析和综合,产生硬件描述语言的文件输出。

8、等待Vivado HLS完成综合,综合完成后会弹出图8.2.9所示的综合报告,其中显示了未做任何优化配置情况下,图8.2.7所示的C语言源码描述的有限冲击响应滤波器所占用的可编程逻辑器件资源、时钟、设计延迟、吞吐量等详细信息。

图8.2.9 综合报告

9、右键单击Explore栏的Test Bench,新建一个测脚本文件,命名为fir_test.c(该文件是图8.1.2所示的“C测试集文件”)。其源码如下。

1 #include代码8.52 #include 3 #include "fir.h" 4 int main () { 5 const int SAMPLES=600; 6 FILE *fp; 7 data_t signal, output; 8 coef_t taps[N] = {0,-10,-9,23,56,63,56,23,-9,-10,0,}; 9 int i, ramp_up;10 signal = 0;11 ramp_up = 1; 12 fp=fopen("out.dat","w");13 for (i=0;i<=SAMPLES;i++) {14 if (ramp_up == 1) 15 signal = signal + 1;16 else 17 signal = signal - 1;18 // Execute the function with latest input19 fir(&output,taps,signal); 20 if ((ramp_up == 1) && (signal >= 75))21 ramp_up = 0;22 else if ((ramp_up == 0) && (signal <= -75))23 ramp_up = 1; 24 // Save the results.25 fprintf(fp,"%i %d %d\n",i,signal,output);26 }27 fclose(fp); 28 printf ("Comparing against output data \n");29 if (system("diff -w out.dat out.gold.dat")) {30 fprintf(stdout, "*******************************************\n");31 fprintf(stdout, "FAIL: Output DOES NOT match the golden output\n");32 fprintf(stdout, "*******************************************\n");33 return 1;34 } else {35 fprintf(stdout, "*******************************************\n");36 fprintf(stdout, "PASS: The output matches the golden output!\n");37 fprintf(stdout, "*******************************************\n");38 return 0;39 }40 }

10、将图8.1.3中所示的“黄金参考”(即算法计算产生的标准答案)out.gold.dat文件拷贝到工程文件中。并用单击Explore栏的Test Bench,将黄金参考添加到工程中。

11、单击工程界面上方的Run C Simulation按钮,进行代码测试。根据上面的fir_test.c测试代码,若代码的运行结果与黄金参考一致,界面下方的Console窗口中将打印出PASS: The output matches the golden output! 的字样。

图8.2.10 C语言测试

12、至此为止,编写的代码所实现的算法如果功能正确,且在占用资源、设计延迟、吞吐量等方面都已经达到了设计目标,则可以导出高层次高层次综合器产生的硬件描述语言代码,以供Vivado在工程中调用该算法。

在Solution菜单中选择Export RTL,在弹出的界面如图8.2.11所示,选择最常用的生成IP方式导出,单击OK,Vivado HLS将产生可供Vivado调用的IP。界面下方的Console窗口中输出Finished export RTL时,就可以在…\solution1\impl\ip文件夹下看到生成的IP.zip文件。

图8.2.11 输出硬件描述语言RTL配置界面

[原创www.cnblogs.com/helesheng]

-

![高层次综合器(Vivado HLS)的设计流程[原创www.cnblogs.com/helesheng]](http://www.jxyuging.com/uploadfile/2022/0923/20220923105321819.jpg)

-

-

-

高层次综合器(Vivado HLS)的设计流程[原创www.cnblogs.com/helesheng]

变天了!x86 PC陨落:ARM大暴走

高通憋出新大招:4G杀手来了

国美电器多个破产申请被驳回 苏泊尔在列

当前关注:脸都不要了!《黑棉花:悟能》无耻碰瓷《黑神话:悟空》

Intel中国特供新U i7-13790F开卖:缓存多3MB 竟贵了150元!

当前快报:【Windows】Microsoft Store无法打开:关闭自动更新(请联系系统管理员更改此设置)

最资讯丨吴京与粉丝合照被滤镜坑惨:没有明星能逃过美颜摧残

环球时讯:明天上映!《流浪地球2》发布港版预告片:MOSS竟然说英文

资讯:log4cxx配置日期回滚策略中增加MaxFileSize属性

天天看点:MySQL索引的基本理解

当前关注:强大的Excel工具,简便Vlookup函数操作:通用Excel数据匹配助手V2.0

通过python,将excel中的数据写入二维列表

天天日报丨爬虫基础

科大讯飞:类ChatGPT技术今年5月落地 AI学习机产品先用

天天速看:31.98万元!理想L7 Air发布:性能不变 无空气悬架

天天速读:三星S23 Ultra拍月亮100倍变焦的效果:把马斯克都惊艳到了

世界今头条!分布式配置nacos搭建踩坑指南(上)

焦点消息!TVS二极管

(七)elasticsearch 源码之元数据CulsterState

暴雪关停国服后 CEO发声:游戏行业被亚洲主宰 东西方竞争不平衡

累计交付27万台 李想:理想成为国内家庭消费者首选豪华SUV

世界最新:高通全球首发5G NR-Light基带:主打中端物联网、峰值速率220兆

城市行驶每公里仅1毛钱!理想L7出行成本不足宝马X5十分之一

消息!drf认证/权限/频率/分页-过滤-排序

报道:【时间基准】NTP网络时钟服务器助力智能农业系统

快播:C和Python实现快速排序-三数中值划分选择主元(非随机)

宗申新款电动车闪电侠发布:续航超200公里 仪表盘可手机投屏

环球观速讯丨丢失两年的手机半夜仍被人试图解锁 被系统远程拍下照片

网友吐槽快递派送延误 韵达总部:人手紧张正调配

《狂飙》蜚声海外 英国小伙们沉迷剧集无法自拔:竟被打斗画面吸引

今日热文:大货车实线变道 女子科三被别停挂科当场发飙

全球热消息:土耳其一城市震后被海水倒灌:汽车泡在水里

环球观焦点:漂浮在数万米高空 你见到的“不明飞行物”:很可能就是一只气球

一加Ace 2支持双频GPS:发布会上没讲 结果被很多网友误伤

【天天播资讯】太火爆!ChatGPT多次因访问量激增而宕机

程序员常用的6款效率工具,准时下班不是梦

世界看点:春节假期“清零”,任务管理飞项快速助你回到高效状态

全球最新:win10系统,软件不可用,无法调用摄像头

Linux内核跟踪和性能分析

要闻:14年了:“千年老二”微软终于有机会扳倒谷歌搜索

热消息:微星推出Cubi 5 12M迷你主机:仅0.66L、配备双网口

世界热点评!女生应聘被问是否单身!当事公司:要求单身正常 将起诉举报者

【全球时快讯】近50年来首次!日本沙滩惊现大量沙丁鱼 原因未知:开排核废水、也要大地震?

最新资讯:国产车开门红:1月比亚迪称王 大众沦落第三 合资腰斩

03-Pandas详解

今日热讯:ChatGPT能做什么?零基础教你免费使用ChatGPT和账号注册

当前速看:美团面试失败后,翻了两年前的面试题,发现根本不是一个难度的

当前简讯:Linux安装

Spring Boot发送GET/POST请求——RestTemplate的基本使用

当前报道:自研指令集没有侵权MIPS 国产CPU龙芯赢了:摆脱官司

当前讯息:自燃车辆引燃邻车 损失谁来赔?法院释疑

天天最新:基于 eBPF 的 Serverless 多语言应用监控能力建设

世界最新:构建亿级别的消息推送基础模型

全球热文:Linux开源工具之nethogs命令介绍

精选!COBOL教程_编程入门自学教程_菜鸟教程-免费教程分享

华硕发布新款Vivobook 13 Slate笔记本:Intel 7W超低功耗U

今日精选:3岁女童喊脚疼被确诊癌症晚期:神经母细胞瘤 儿童癌症之王

天天微速讯:剧版《三体》弹幕互动量破2000万!豆瓣涨至8.3分

【热闻】iPhone 15 Ultra狂堆料!价格可能贵出天际

环球热议:全球不足50人!宝鸡发现1例罕见黄金血型:比熊猫血更稀有

环球资讯:ASP.Net Core 教程_编程入门自学教程_菜鸟教程-免费教程分享

ChatGPT保姆级注册教程

group by 、concat_ws()、 group_caoncat()的使用

全球热头条丨Jedis那么低性能,还在用吗? lettuce时代开幕啦

热资讯!阿里IM技术分享(十):深度揭密钉钉后端架构的单元化演进之路

强震已致超7700人遇难!土耳其地震背后的人祸 建筑不达标、豆腐渣工程多

全球热议:全球首架国产大飞机C919首飞三亚 民航最高接待礼“过水门”接风

环球关注:iPhone 15 Pro系列拿到三星顶级屏幕!超出S23系列整整两代

全球消息!高级Excel教程_编程入门自学教程_菜鸟教程-免费教程分享

重点聚焦!Serverless 时代开启,云计算进入业务创新主战场

【天天报资讯】Go的参数是传值还是传引用问题

【环球聚看点】【踩坑记录】单测中@PostConstruct多次执行

免费无广告 微软电脑管家2.7公测版发布:任务栏被意外修改有救了

4599元!佳能EOS R50发布:329克超轻便 支持无裁切6K

天天信息:研发10几年、花费千亿:日本国产大飞机为何失败?就是畸形产物

全球微速讯:LV将涨价?国人排长龙抢购 买万元包像在赶集:世界首富曾感慨中国用户有钱

高级Excel图表教程_编程入门自学教程_菜鸟教程-免费教程分享

Apache ANT 教程_编程入门自学教程_菜鸟教程-免费教程分享

焦点播报:算法学习笔记(15): Trie(字典树)

今日讯!火山引擎 DataTester“智能发布”:覆盖产品研发、测试、上线全流程,一站式智能管理 A/B 实验

DB2教程_编程入门自学教程_菜鸟教程-免费教程分享

马斯克将于3月1日公布特斯拉宏图第三篇章 第二篇章已烂尾

世界观速讯丨国产车企1:1复刻几十年前的MINI外观专利 宝马抗议!结果判了

【独家焦点】真心没想到!五旬男子开车撞上护栏:只因刚割了双眼皮

全球热消息:全世界最后一只袋狼究竟是怎么死的?

民企第一只 京东仓储REIT上市:认购额超718亿元遭疯抢

当前视讯!C#(进制转换) NumberConversion

ChatGPT国内也能用吗?ChatGPT国内镜像站点分享给你们

微动态丨暴躁小钢炮!极氪X实车亮相:零百加速3秒级

环球微速讯:《仙剑奇侠传》《和平精英》梦幻联动:赵灵儿端枪吃鸡

啥身材都能包!真维斯连帽卫衣大促:日常100元 现价50到手

6年来苹果iPhone涨价近50% 还会继续涨 库克不怕没人买

《流浪地球2》导演郭帆:国产科幻片工业流程还是初级 吃饭都会出大错误

童话二分之一的大结局是什么?童话二分之一演员表

金棕色适合什么肤色?金棕色和金栗色茶色的区别有哪些?

回避型人格障碍的表现有哪些?回避型人格障碍怎么治疗?

天天快资讯丨袋鼠云数栈UI5.0焕新升级,全新设计语言DT Design,更懂视觉更懂你!

【世界热闻】芯驿电子发布车载系列产品全新品牌AUMO

速讯:仿制作图《这里是中国》封面