最新要闻

- 天天观焦点:女子有洁癖:每天消杀双手10次 结果患乏脂性皮炎

- 最新快讯!彻底消灭自燃!宝马今年开始测试固态电池:计划两年后装车

- 世界信息:情人节倒计时 国外动物园想出报复前任的绝妙点子:蟑螂惨了

- 当前速讯:宏碁杀入显卡市场!通吃Intel/AMD、不碰NVIDIA

- 新资讯:《狂飙》热播!湖南一网吧凌晨变《狂飙》专场

- 中国新车质量榜:前四均被合资车企包揽 本田最大赢家

- 刷新中国影史记录!2023年院线全年总票房已破百亿

- 播报:男生和女生初四相亲初八订婚:称不想耽误节后上班!网友惊到

- 全球热头条丨《黑豹2》中国角色海报发布:全员黑色皮肤 2月7日上映

- 看点:我国自研水陆飞机!“鲲龙”AG600M全面进入型号取证试飞阶段

- 每日视讯:有博主称《满江红》制作成本不到1000万!歌手胡彦斌一番话上了热搜第一

- 视焦点讯!Xbox月活用户突破1.2亿!微软赢麻了

- 全球快看:强盛集团橱窗上架《孙子兵法》:还卖小灵通手机壳

- 迄今为止最庞大的公版显卡来了?RTX 4090Ti/Titan曝光

- 比亚迪正式进军日本市场卖车:“两田一产”如临大敌

- 每日快报!首款车明年量产!小米汽车最新专利公布:手表控制车有戏

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

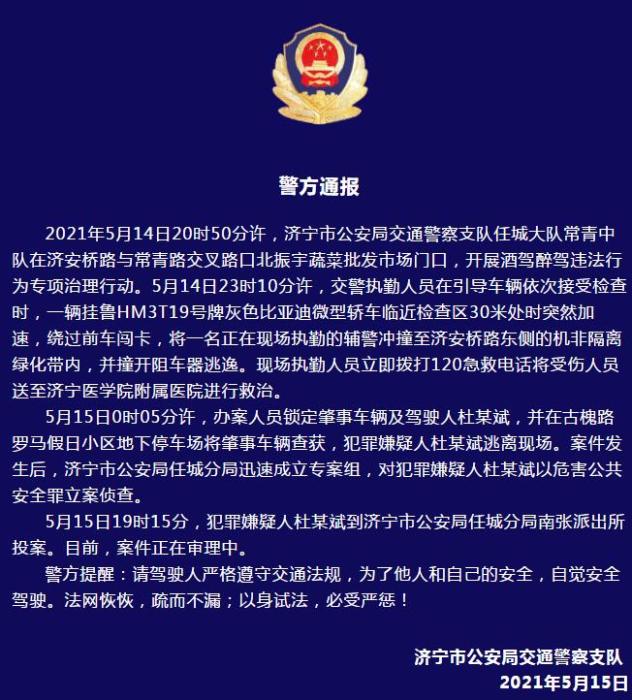

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

DDS结构的FPGA实现

【资料图】

【资料图】

一、DDS工作原理

- 以正弦信号为例,DDS大概就是将M个点的一个周期的正弦序列存入ROM中,序列数据的地址就是正弦信号的相位;

- 通过修改频率控制字(Fword)来改变每隔多少个地址取ROM里的数据进行输出。频率控制字越大,从ROM取出的数据点就越少,点数越少,输出一个周期信号的时间就越短,从而改变了输出信号的频率;

- 通过修改相位控制字(Pword)来改变读取ROM里的数据的初地址(就是给ROM地址增加偏移量),从而改变输出信号的初相。DDS的基本结构图如下图所示:输出信号的频率的公式为:其中\(F_{CLK}\)为模块的时钟频率,\(F_{Word}\)为频率控制字,N为频率控制字的位宽。

二、模块代码

关于ROM的配置可以点击此处。

`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company: GDUT// Engineer: Lclone// // Create Date: 2023/01/30 19:11:43// Design Name: DDS_Base// Module Name: DDS_Base// Project Name: DDS_Base// Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision:// Revision 0.01 - File Created// Additional Comments:// //////////////////////////////////////////////////////////////////////////////////module DDS_Base( input Clk, input Rst_n, input [31:0] Fword, input [11:0] Pword, output [ 7:0] Signal_data ); reg [31:0] Fword_r; always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) Fword_r <= 0; else Fword_r <= Fword_r + Fword; end reg [11:0] ROM_addr; always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) ROM_addr <= 0; else ROM_addr <= Fword_r[31:20] + Pword + 1"b1; end ROM_Sinwave ROM_Sinwave_inst( .clka (Clk), .addra (ROM_addr), .douta (Signal_data)); endmodule三、仿真

1、仿真代码

在分析频率的时候例化一个该模块分析就行,在分析相位时候例化两个模块进行对比即可下面给出分析相位时候的仿真文件:

`timescale 1ns / 1psmodule DDS_Base_tb();reg clk_50m;initial clk_50m <= 0;always #10 clk_50m <= ~clk_50m;reg rst_n;initial begin rst_n <= 0; #200 rst_n <= 1;endreg [31:0] FwordA;reg [11:0] PwordA;wire[ 7:0] Signal_dataA;reg [31:0] FwordB;reg [11:0] PwordB;wire[ 7:0] Signal_dataB;initial begin FwordA <= 0; PwordA <= 0; FwordB <= 0; PwordB <= 0; #300 FwordA <= 1024*1024*2; //情况1 PwordA <= 0; FwordB <= 1024*1024*2; PwordB <= 4096/4 - 1; //相移90° #163840 FwordA <= 1024*1024*4; //情况2 PwordA <= 0; FwordB <= 1024*1024*4; PwordB <= 4096/2 - 1; //相移180° #163840 FwordA <= 1024*1024*0.5;//情况3 PwordA <= 0; FwordB <= 1024*1024*0.5; PwordB <= 4096/2 - 1; //相移180° #163840 #100 $stop;endDDS_Base DDS_Base_A( .Clk (clk_50m), .Rst_n (rst_n), .Fword (FwordA), .Pword (PwordA), .Signal_data (Signal_dataA) ); DDS_Base DDS_Base_B( .Clk (clk_50m), .Rst_n (rst_n), .Fword (FwordB), .Pword (PwordB), .Signal_data (Signal_dataB) ); endmodule3、仿真分析

频率分析

整体波形如下图所示:情况1:此时频率控制字设置为102410242,根据公式算得频率为24,414Hz,周期为40.96us,与仿真结果41us相近。情况2:此时频率控制字设置为102410244,根据公式算得频率为48,828.125Hz,周期为20.48us,与仿真20.4889us结果相近。情况3:此时频率控制字设置为102410240.5,根据公式算得频率为6,103.51Hz,周期为163.84us,与仿真163.8405us结果相近。

相位分析

结论:仿真通过,该DDS模块能够调节输出信号的频率和初相。

四、参考资料

[1]【零基础轻松学习FPGA】小梅哥Xilinx FPGA基础入门到项目应用培训教程

-

-

【算法训练营day34】LeetCode1005. K次取反后最大化的数组和 LeetCode134. 加油站 LeetCode135. 分发糖果

LeetCode1005 K次取反后最大化的数组和题目链接:1005 K次取反后最大化的数组和独上高楼,望尽天涯路...

来源: -

-

DDS结构的FPGA实现

【算法训练营day34】LeetCode1005. K次取反后最大化的数组和 LeetCode134. 加油站 LeetCode135. 分发糖果

天天观焦点:女子有洁癖:每天消杀双手10次 结果患乏脂性皮炎

最新快讯!彻底消灭自燃!宝马今年开始测试固态电池:计划两年后装车

世界信息:情人节倒计时 国外动物园想出报复前任的绝妙点子:蟑螂惨了

当前速讯:宏碁杀入显卡市场!通吃Intel/AMD、不碰NVIDIA

新资讯:《狂飙》热播!湖南一网吧凌晨变《狂飙》专场

实时焦点:如何手动补充陈年老库(或纯 JS 代码)的 TypeScript 类型?

中国新车质量榜:前四均被合资车企包揽 本田最大赢家

刷新中国影史记录!2023年院线全年总票房已破百亿

播报:男生和女生初四相亲初八订婚:称不想耽误节后上班!网友惊到

全球热头条丨《黑豹2》中国角色海报发布:全员黑色皮肤 2月7日上映

看点:我国自研水陆飞机!“鲲龙”AG600M全面进入型号取证试飞阶段

博客园主题美化DIY教程

全球短讯!优秀前端都应该具备的开发好习惯,坚持了效率翻倍

每日视讯:有博主称《满江红》制作成本不到1000万!歌手胡彦斌一番话上了热搜第一

视焦点讯!Xbox月活用户突破1.2亿!微软赢麻了

全球快看:强盛集团橱窗上架《孙子兵法》:还卖小灵通手机壳

迄今为止最庞大的公版显卡来了?RTX 4090Ti/Titan曝光

比亚迪正式进军日本市场卖车:“两田一产”如临大敌

世界消息!Linux 服务器Python后台运行服务(ssh断开不退出)

资讯推荐:Docker-consul的容器服务更新与发现

【天天时快讯】记录--手把手教学,实现一个优雅的图片预览

每日快报!首款车明年量产!小米汽车最新专利公布:手表控制车有戏

天天热文:A卡游戏画面鲜艳 N卡灰蒙蒙?可能是这里设置错了

焦点播报:北美杀入前十后《流浪地球2》官宣:2月9日在中国香港及澳门上映

焦点简讯:三体人为什么那么害怕地球人的加速器?中科院科普

中国航天科技喊话《流浪地球2》:太空天梯、地球车站、空间驿站有望实现

全球报道:网易二面:CPU狂飙900%,该怎么处理?

每日看点!男子打赏女主播1.8万后起诉欲要回!最终被驳回诉求

焦点速递!男子寄5万元笔记本被摔坏索赔遭拒:屏幕、键盘都烂了 维修要2万

动视暴雪点赞《最后生还者》:索尼令人敬畏 我们被收购是应该的

天天热头条丨官网12.4万元帕纳梅拉遭抢购 保时捷:情况属实 已与首单用户达成协议

当前观察:索尼PS5现货全开放!黄牛惨了:带大量机器退货遭拒

环球资讯:Redis数据结构实战演练,看看微博、微信、购物车、抽奖小程序是如何使用的?

全球聚焦:【促进开发】上海道宁与DHTMLX为您提供易于使用且功能丰富的JavaScript组件

APITable:免费开源的多维表格与可视化数据库,上线1天斩获GitHub星标1000+

今日精选:HTTP笔记1--网络模型

环球速讯:selenium + python自动化测试环境搭建

刘慈欣:30年前拍不成《流浪地球2》 投资人不会信的

观热点:SSD性能领先35倍 机械硬盘命悬一线:没啥理由买

【全球速看料】流浪小狐狸投奔看守所1年胖成球:今年要帮它减肥

不止砍掉UFS 4.0:三星Galaxy S23标准版遭全方位缩水

c++代码实现中时间复杂度的不断优化

聚焦:一步一步实现若依框架--2.4数据权限 data_scope

800W功耗!RTX 4090 Ti四插槽"核弹"真的有 但不一定能生出来

全球微速讯:《最后生还者》剧集第3集与游戏对比 还原度高

实时焦点:摩托骑手广东高速上恶意损坏其他车辆 官方回应:一刀切禁摩很好?

天天观察:云萌 V2.6.3.0 win10,win11 Windows永久激活工具

热推荐:基于Spring Cache实现Caffeine、jimDB多级缓存实战

portswigger 靶场之 XSS 篇 (下)

全球最新:【算法训练营day32】LeetCode122. 买卖股票的最佳时机II LeetCode55. 跳跃游戏 LeetCode45. 跳跃游戏II

部署Kubernetes Cluster

每日短讯:12.4万买新帕纳梅拉!近600名国内网友保时捷官网疯抢:成功下单后被取消

【全球时快讯】奔驰获全球首家L3级自动驾驶认证:开车不用看路 出事故奔驰负责

【快播报】优酷回应1元会员被扣24元争议:活动规则已告知 扣钱没毛病

当前热文:水墨风场景惊艳!《仙剑奇侠传7》DLC《人间如梦》官宣2月发售

彻底扑灭一台特斯拉Model S有多难 消防员实测:用了22.7吨水

天天快消息!Android 软键盘丝滑切换(一)

天天看点:视频发布失败原因不好找?火山引擎数智平台这款产品能帮忙

速看:OpenYurt v1.2 新版本深度解读(一): 聚焦边云网络优化

【环球播资讯】小鹏股价暴跌、交付量惨淡 何小鹏专访回应:未来会这么做

全球动态:全球首个!婴幼儿视功能损伤手机智能筛查系统面世

撸猫手感 绿联iPhone 12-14系列液态硅胶保护壳9.9元起

天天快看点丨海淘不香了!日版Xbox主机涨价将近260元

天天速递!全国首烧?疑似红旗E-HS9充电时起火 现场黑烟弥漫

瑾娘为什么要杀华裳?瑾娘为什么假扮巽芳?

爱在旅途大结局是什么?爱在旅途剧情介绍

法国属于西欧还是北欧?南欧包括哪些国家?

荷兰为什么被称为水之国?荷兰水之国的资料简介

长宽高的英文缩写分别是什么?长宽高怎么算平方?

oppor7手机版本低怎么升级?oppo r7手机参数

复工第一天:请马上卸载这个恶心的软件!!!

全球看热讯:python-paramiko操作的封装

无法定位序数是什么意思?无法定位序数怎么解决?

打印机驱动在电脑哪里找?如何卸载打印机驱动?

无线适配器或访问点有问题是什么意思?无线适配器或访问点有问题怎么处理?

魅族手机怎么样?魅族手机锁屏密码忘了怎么解开?

环球速讯:工信部明天起优化调整微波频率 为5G/6G预留频谱资源

【独家】美国下手真狠!沃尔沃在美被罚8.7亿元 史上最大

快消息!APP竟比线下贵一倍还多 有电影院劝说观众退订淘票票

【世界快播报】提车1周 一特斯拉高速上行驶时方向盘脱落:维修还被收费

每日速读!全球最大游戏展E3辉煌不在:微软索尼任天堂“御三家”将集体缺席

波司登云原生微服务治理探索

今日热门!元宵节将至!元宵夜将出现年度最小满月

世界实时:侄子出演叔叔 MJ传记片年内开拍

【速看料】女子抱娃人肉占车位 还移走路障为自家车开路 结局引人舒适

世界讯息:西安阿房宫站将更名西安西站:原西站不够西

天天观热点:猪肉含量≥85% 一口全是肉:亚明猪肉烤肠2斤29.9元大促

焦点要闻:读Java8函数式编程笔记06_Lambda表达式编写并发程序

【全球新要闻】全网影视免费看,最新电影、电视剧免广告免VIP观看,只要你能搜到的,统统都能看,《狂飙》、《三体》追剧神器,时刻掌握最新剧集,无需安装,使用简单,

被苹果踢出供应链两年了 欧菲光仍未缓过劲:2022巨亏40多亿

精选!疯狂玩梗!强盛集团孙红雷直播被买鱼刷屏

焦点短讯!A卡很难追 游戏开发者越来越喜欢DLSS:理由离谱 弥补D加密损失

环球即时看!2023春节档爆发:复苏满座与极端的粉黑大战

每日消息!关于桌面上一万多个图标

刘慈欣:30年前拍不成《流浪地球2》 投资人不信中国有太空电梯

世界快看:老外幸福感暴降:英国近半年轻人担心收入永远不够养家

别贪速度快!SSD选什么接口更适合你?

《敢死队2》观后感