最新要闻

- 中国驻洛杉矶总领馆提醒中国公民防范电信诈骗

- 世界热推荐:小米机皇赢麻了!13 Ultra京东好评率超过99%

- 纯白千层镜!影驰RTX 4060 Ti 8GB星曜OC图赏

- 员工每天带薪上厕所3至6小时被解雇:法院判了 环球热闻

- 【天天快播报】618首销第一天Redmi霸占预售榜前三名 卢伟冰:孤独

- 这对中意“姐妹”世界遗产地 共话生态保护_世界微动态

- 韩一季度总和生育率0.81 创历年同期最低

- 天天讯息:2149元太香了!AMD RX 7600正式发布:最高提速55%

- 硬刚RTX 4060!AMD RX 7600图赏|世界新视野

- 焦点热议:两对情侣因争位置在迪士尼起冲突:双方已调解

- 老外吐槽RTX 4060 Ti/RX 7600:2023年了 2000多元还是1080P游戏显卡

- 天天看热讯:白色机身玩趣十足!索泰RTX 4060 Ti X-GAMING显卡图赏

- 辽宁沈阳一老人乘坐地铁禁止周边人玩手机 称辐射会导致自己眼睛模糊

- 《闪电侠》电影曝光IMAX和杜比影院海报 继续由埃兹拉·米勒饰演

- 电影《速度与激情10》上映7天 总票房破6亿,

- 杨紫琼主演《西游ABC》现已正式播出 为迪士尼+原创奇幻动作喜剧

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

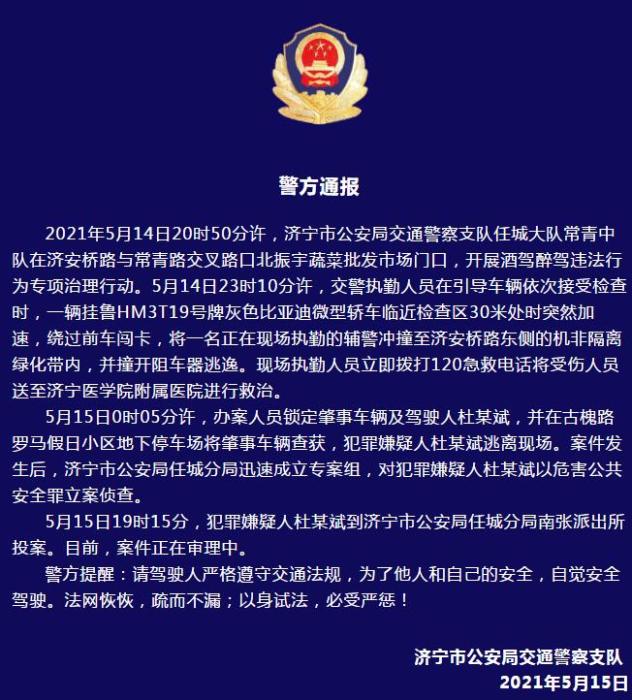

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

全球今日讯!10-阻塞赋值和非阻塞赋值

【资料图】

【资料图】

1.阻塞赋值和非阻塞赋值

阻塞赋值的赋值号用"="表示,对应的电路结构往往与触发边沿没有关系,只与输入电平的变化有关系,它的操作可以认为是只有一个步骤的操作,即计算赋值号右边的语句并更新赋值号左边的语句,此时不允许有来自任何其他verilog语句的干扰,直到现行的赋值完成,才允许下一条的赋值语句执行串行块(begin end)中,各条赋值语将以它们在顺序块中的排列次序依次执行

a = 1;b = 2;c = 3;begin a = b + 1; // a = 3 b = a + 2; // b = 5 c = a - 1; // c = 4end非阻塞赋值的赋值号用"<="表示,对应的电路结构往往与触发沿有关系,只有在触发沿的时刻才能进行非阻塞赋值;非阻塞赋值操作可以看作是两个步骤的过程:在赋值开始时刻,计算赋值号右边的语句(所有赋值号右边的结果),在赋值结束时刻(end),更新赋值号左边的语句在计算非阻塞赋值号右边的语句和更新赋值号左边语句期间,允许其他的verilog语句同时进行操作非阻塞赋值只能用于寄存器类型变量进行赋值,因此只能用于initial语句和always语句,不允许用于连续赋值语句assign

a = 1;b = 2;c = 3;begin // 开始 结束 a <= b + 1; // 三条语句并行执行 3 3 b <= a + 2; // 3 3 c <= a - 1; // 0 0end 2.实践

2.1 阻塞赋值

module blocking( input wire sys_clk, input wire sys_rst_n, input wire [1:0] in, output reg [1:0] out); // 定义中间变量 reg [1:0] in_reg; always@(posedge sys_clk or negedge sys_rst_n) begin if(sys_rst_n == 1"b0) begin in_reg = 2"b0; out = 1"b0; end else begin in_reg = in; out = in_reg; end endendmodule- 创建quartus工程,进行编译

`timescale 1ns/1nsmodule tb_blocking(); reg sys_clk; reg sys_rst_n; reg [1:0] in; wire [1:0] out; // 初始化时钟和复位信号,输入信号 intial begin sys_clk = 1"b1; sys_rst_n <= 1"b0; in <=2"b0; #20; sys_rst_in = 1"b1; end // 模拟时钟 initial begin #10; sys_clk = ~sys_clk; end always #10 in <= {$random} % 4; // 生成非负数0,1,2,3 blocking block_inst( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .in (in), .out (out) ); endmodule2.2 非阻塞赋值

module nonblocking( input wire sys_clk, input wire sys_rst_n, input wire [1:0] in, output reg [1:0] out); // 定义中间变量 reg [1:0] in_reg; always@(posedge sys_clk or negedge sys_rst_n) begin if(sys_rst_n == 1"b0) begin in_reg <= 2"b0; out <= 1"b0; end else begin in_reg <= in; out <= in_reg; end endendmodule- 当想要对想要的信号打两拍的时候,使用非阻塞赋值

- 时序逻辑电路使用非阻塞赋值,组合逻辑电路使用阻塞赋值

- always语句块实现组合逻辑,使用阻塞赋值,不能即使用阻塞赋值又使用非阻塞赋值

- 避免锁存器latch,使用锁存器的时候使用非阻塞赋值的方式

- 一个always语句块只对一个变量进行赋值

关键词:

-

-

-

-

全球今日讯!10-阻塞赋值和非阻塞赋值

中国驻洛杉矶总领馆提醒中国公民防范电信诈骗

世界热推荐:小米机皇赢麻了!13 Ultra京东好评率超过99%

纯白千层镜!影驰RTX 4060 Ti 8GB星曜OC图赏

员工每天带薪上厕所3至6小时被解雇:法院判了 环球热闻

【天天快播报】618首销第一天Redmi霸占预售榜前三名 卢伟冰:孤独

精彩看点:Java设计模式-享元模式

这对中意“姐妹”世界遗产地 共话生态保护_世界微动态

多地加快推进基础设施工程建设

韩一季度总和生育率0.81 创历年同期最低

天天讯息:2149元太香了!AMD RX 7600正式发布:最高提速55%

硬刚RTX 4060!AMD RX 7600图赏|世界新视野

焦点热议:两对情侣因争位置在迪士尼起冲突:双方已调解

老外吐槽RTX 4060 Ti/RX 7600:2023年了 2000多元还是1080P游戏显卡

天天看热讯:白色机身玩趣十足!索泰RTX 4060 Ti X-GAMING显卡图赏

辽宁沈阳一老人乘坐地铁禁止周边人玩手机 称辐射会导致自己眼睛模糊

《闪电侠》电影曝光IMAX和杜比影院海报 继续由埃兹拉·米勒饰演

电影《速度与激情10》上映7天 总票房破6亿,

杨紫琼主演《西游ABC》现已正式播出 为迪士尼+原创奇幻动作喜剧

游客意外掉到野生大黄鱼 在阳光照耀下十分耀眼

徐克导演《射雕英雄传侠之大者》获得2023重点档期推荐影片 由肖战主演

为进一步激活汽车消费 宁波市实施社会车辆提前淘汰财政奖励补贴

杭州一宝妈因网红穿着产生不满 担心对孩子的心理产生不良影响

网易于多伦多和蒙特利尔成立新的游戏工作室 将开发首款开放世界游戏

马斯克称自己的时间管理安排非常困难 现已确定一位接班人

环球今热点:押上一切声誉!小米汽车2024年量产 雷军:今年一季度投入11亿

营收大跌45.9% 小鹏汽车1季度财报公布 CEO放豪言:G6将成爆款

出现重大风险至股价大幅下跌?科大讯飞:谣言 AI“搞的” 今日观点

支持录音实时转写!讯飞录音降噪会议耳机iFLYBUDS Nano+图赏

累计已发21版驱动!Intel:Arc显卡将持续针对DX9/11/12优化

上海沿浦最新公告:拟定增募资不超过3.9亿元-天天讯息

c#中用System.Diagnostics.Process.Start(Path.GetFullPath(“vlc.exe.lnk“), url);用vlc的

Java 创建/识别条形码

前沿资讯!3DS在线商店关闭后:任天堂新补丁堵死破解可能

甲醇汽车:想说爱你 却怕“中毒”!这四点无解

捷克开发者新技术:改变游戏/电影种族 让黑人变白人_全球快看点

全球视讯!金光灿灿真耀眼!游客钓上野生大黄鱼:市场价过万元

今日观点!1899元 米家智能跑步机上架:降噪无刷电机、全跑道设计

又什么又什么的词语大全 又什么又什么的词语

焦点速讯:会话控制

2023年5月24日正己酸价格最新行情预测|时讯

环球快看:小米组建AI实验室大模型团队:AI领域人员已超1200人

大的要来了!国产3A大作《黑神话:悟空》官方B站上号|世界时讯

天天热点评!多品牌多口味正大促! 真真老老地道嘉兴肉粽:四枚9.9元

每日时讯!浙江宁波老旧车辆淘汰补贴:单车最高可补5.7万元

小米13系列成了!在安卓4000-5000价位份额第一名

小花猪Ai绘画!粉红色的回忆,粉红色的我!记忆有你也有我! 热消息

天天精选!功能安全、预期功能安全与信息安全的差异与协同

智慧黄河:实现流域智能化管理的关键一步|环球报资讯

全球实时:记录--按钮级别权限怎么控制

全球观点:债市日报:5月24日

弘扬绿色健康饮食文化-热闻

天天信息:热搜第二!网友月薪5000两年存了8万元:分享7个实用存钱技巧

卖一个赚46块!激光雷达首次盈利 禾赛科技:感谢理想 世界时讯

实时:清新口气 有效抑菌!纳美亮白牙膏:6支仅14.9元

里程碑!小米宣布:MIUI全球月活用户突破6亿

环球新资讯:距离月面10米失联!NASA:日本登月失败登月舱残骸或找到

未能封送类型,因为嵌入数组实例的长度与布局中声明的长度不匹配 全球微头条

理解JS中的Promise

一步步完整搭建一个图纸管理系统(Django+Vue3)

【MyBatis】saveBatch 性能调优|即时焦点

世界观点:被曝北约考虑在日设联络处后,岸田宣称日本没有加入北约计划

苦等几十年!Windows终于原生支持rar、7z等格式压缩文件了|全球视点

车标贴满全身!梅赛德斯-迈巴赫Night Series官图发布:真奢华

【全球聚看点】699元 联想YOGA K7机械键盘上架:82键矮轴 真空电镀工艺

AI网聊10分钟被骗430万 中国互联网协会给出防范建议

环球今头条!国内多航司现千元内国际机票 上海直飞日本仅600元

西部决赛:掘金淘汰洛杉矶湖人的背后,藏着多少鲜为人知的秘密-热消息

es之增删改查 每日播报

顶象全新金融业务安全方案,亮相亚太银行数字化峰会

Java开启异步的两种方式

Python文件读写、StringIO和BytesIO_每日速看

动态:Ruby教程_编程入门自学教程_菜鸟教程-免费教程分享

【环球新要闻】【新华500】新华500指数(989001)24日下跌1.28%

安卓不再清后台 OPPO Reno10系列用上16GB大内存:48个月流畅

Find系列同款!OPPO Reno10 Pro搭载动态光影屏:120Hz高刷

视点!不怕别人超越!“比亚迪魔方”储能系统发布:首搭刀片电池

环球新消息丨349元 OPPO Enco R2耳机发布:Hi-Fi级处理芯片

支付宝提醒“学生账户升级”骗局:没有学生/成人账户概念!

焦点快播:Spring Boot 我随手封装了一个万能的 Excel 导出工具,传什么都能导出!

火山引擎DataLeap联合DataFun发布《数据治理知识地图》_世界新消息

当前要闻:推荐一个AI导航网站 - 收录的都是热门AI工具

社区工作者感受垃圾分类处理全过程

北京西京医院杨博华_北京西京医院

64核CPU、显卡三连冠 AMD超算屠榜:唯一一台百亿亿次

国产SSD卷疯了!梵想S500 Pro 2TB只要409元 观天下

最轻薄潜望手机!OPPO Reno10 Pro+亮相

当前关注:搭载4.0L水平对置发动机 300万的保时捷中国开卖:但不能上路

淮北建投20亿元公司债将付息 利率6.30%

springboot~mybatis-plus的DynamicTableNameInnerInterceptor实现分表

用上3.0T直六发动机!马自达旗舰CX-90现身:今年内国产_天天看热讯

今日播报!Win11最新版发布:性能更好更丝滑

粤港澳大湾区首个京粤产业协作中心挂牌并落户广州黄埔 快播报

苹果WWDC23终极“剧透”:iOS 17登场 首款头显万众期待 天天精选

天天热点评!《原神》3.7版本正式上线!原神首个卡牌赛事登场

99包邮手慢无!匹克路威篮球鞋2折清仓(门店469元)

脾气真大!一特斯拉插队未遂现场报复:直接加速撞车 全球快看

甄子丹出演苹果广告:叶师傅 切他中路!|当前焦点

焦点播报:“五一”假期出行,伴随着哪些风险

全网最全的编程电子书大合集,超千本打包下载