最新要闻

- 今日热议:南钢股份:钢材销量同比下降6.28%,2022年年归母净利润同比下滑48.59%,拟10派2.5元

- 快讯:《生化危机4:重制版》D加密惹争议 又导致性能问题了

- 全球观热点:女子地铁照被AI一键脱衣传播 网友:无下限的开发

- 每日焦点!网友准备冲Redmi Note 12 Turbo哈利·波特版:预算3900元

- 头条:男子乘错出租车 起步1秒被强制收费6元:走了不到10米

- 【世界新视野】内存掉入无底洞:没有最便宜 只有更便宜

- 全球看点:乒乓球技巧训练这就是高手的水准_乒乓球技巧

- Twitter将上线离谱新规:非会员甚至无法参与投票

- 热头条丨九识自动驾驶物流车被曝闯红灯 网友:该怎么记分处罚

- 速读:“网红”威震天在北京环球影城摔了一跤 客服回应:后续演出正常

- 【环球新要闻】一个时代结束了!Wii U和3DS在线商店已正式关闭

- 实时:透明外壳设计!Nothing Ear(2)无线耳机上市 999元

- 环球观焦点:韩国有意解禁福岛水产品?在野党呼吁韩总统表态

- 全球热头条丨想玩必须升级!Steam将于2024年终止对Win7/8/8.1系统支持

- 中国科学家发现月球水库 估计蓄水量多达2700亿吨

- 父母做生意给儿子取名为顾客 当事人:家里有个“顾客”能带来更多顾客

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

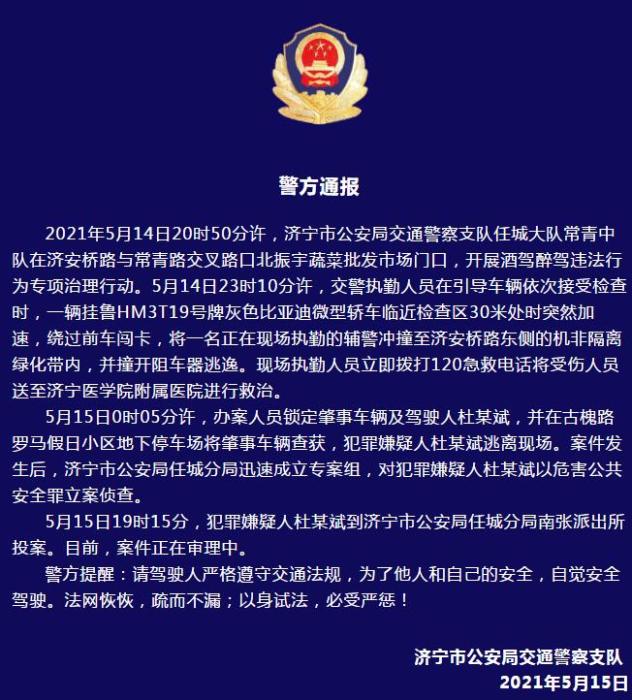

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

全球关注:借助 mperf 进行矩阵乘法极致优化

作者:旷视 MegEngine 架构师 洪超

前言

单精度矩阵乘法(SGEMM)是非常典型的计算密集型算子,对 SGEMM 的优化也经常被当作算子优化从业人员的练手项目。本文将借助于 mperf,在 ARM A55 cpu 核心上对 SGEMM 的性能进行极致优化,过程中会展示 mperf 辅助性能优化工作的基本逻辑。希望本文的读者对计算机体系结构有一定了解,并且可以补充一些 TMA 的基础概念。另外,关于本文使用的 mperf 工具,更多详细介绍请参见之前的文章 mperf 介绍。

本文需要优化的计算目标是 C=AB,假设矩阵 A 大小为 MK,矩阵 B 大小为 KN,则得到矩阵 C 大小为 MN 。为了后文分块操作的方便,这里假设 M,N 是 4 的倍数,并选择 M=N=K 分别为 100,200,300,500,700,900 的矩阵尺寸,对不同优化版本进行性能测试。本文所有试验代码均在 mperf/apps/cpu_pmu_analysis 目录下。

(资料图片)

(资料图片)

矩阵乘法优化

寄存器和 FPU 优化——Naive 实现到循环展开

矩阵乘法的 Naive 实现为三层循环计算:

//lda:number of columns of A //ldb:number of columns of B//ldc:number of columns of C #define A(i, j) a[(i)*lda + (j)]#define B(i, j) b[(i)*ldb + (j)]#define C(i, j) c[(i)*ldc + (j)]void my_matmul_naive(int m, int n, int k, float* a, int lda, float* b, int ldb, float* c, int ldc) { int i, j, p; for (i = 0; i < m; i++) { for (j = 0; j < n; j++) { for (p = 0; p < k; p++) { C(i, j) = C(i, j) + A(i, p) * B(p, j); } } }}此时,测试 M=N=K 分别为100,200,300 时的 mperf 性能数据见 Naive_mperf , 关于这些测试数据的简单介绍请参见 mperf 测试数据。测试命令(后文其他优化版本的测试命令不再重复贴出):

First, compile the testcase, using `/android_build.sh -m arm64-v8a`.Then, copy build_dir/apps/arm_cpu_matmul_naive to your android platform, and run it.从上面链接的 mperf 数据可以看到 Naive 实现的 GFLOPS 甚至不到 0.5,而 mperf 在 ARM A55 平台实测的峰值浮点算力可以达到 14GFLOPs,显然我们还有很长的路要走。

分析 TMA Level-1 的数据,也即比较 Frontend_Bound、Bad_Speculation、Backend_Bound 和 Retiring 的占比,可以发现占比最高的为 Backend_Bound,约为 50%,据此首先可以判断 Naive 版本的性能瓶颈位于处理器后端。进一步看 TMA Level-2 及以上级别的数据,发现 Backend_Bound 中占比最大的是 Core_Bound ,而 Interlock_Bound 又占 Core_Bound 的 95% 以上,紧接着 Interlock_FPU 又几乎占 Interlock_Bound 的 100%。

由此可得,当前的瓶颈在于 Interlock_FPU,Interlock_FPU 占比大说明浮点计算触发了大量的 pipeline stall。除此之外,我们还观察到 Metric_Neon_Port_Util 为 0,这是因为 Naive 版本没有进行向量计算。

关于如何降低 Interlock_FPU,我们早期基于 mperf 做过验证,证明 unroll 可以有效降低 Interlock_FPU,过程如下:

#define UNROLL_RAW1(cb, v0, a...) \ cb(0, ##a) #define UNROLL_RAW2(cb, v0, a...) \ cb(0, ##a) cb(1, ##a) #define UNROLL_RAW5(cb, v0, a...) \ cb(0, ##a) cb(1, ##a) cb(2, ##a) cb(3, ##a) cb(4, ##a)#define UNROLL_RAW10(cb, v0, a...) \ UNROLL_RAW5(cb, v0, ##a) \ cb(5, ##a) cb(6, ##a) cb(7, ##a) cb(8, ##a) cb(9, ##a)#define UNROLL_RAW20(cb, v0, a...) \ UNROLL_RAW10(cb, v0, ##a) \ cb(10, ##a) cb(11, ##a) cb(12, ##a) cb(13, ##a) cb(14, ##a) cb(15, ##a) \ cb(16, ##a) cb(17, ##a) cb(18, ##a) cb(19, ##a)#define UNROLL_CALL0(step, cb, v...) UNROLL_RAW##step(cb, 0, ##v)#define UNROLL_CALL(step, cb, v...) UNROLL_CALL0(step, cb, ##v)#define THROUGHPUT(cb, func, UNROLL_NUM) \ static int func##_throughput_##UNROLL_NUM() { \ asm volatile( \ UNROLL_CALL(UNROLL_NUM, eor) \ "mov x0, %x[RUNS]\n" \ "1:\n" \ UNROLL_CALL(UNROLL_NUM, cb) \ "subs x0, x0, #1 \n" \ "bne 1b \n" \ : \ : [RUNS] "r"(mperf::RUNS) \ : "cc", "v0", "v1", "v2", "v3", "v4", "v5", "v6", "v7", "v8", "v9", \ "v10", "v11", "v12", "v13", "v14", "v15", "v16", "v17", "v18", \ "v19", "x0"); \ return mperf::RUNS * UNROLL_NUM; \ }#define cb(i) "fmla v" #i ".4s, v" #i ".4s, v" #i ".4s\n"THROUGHPUT(cb, fmla, 20)THROUGHPUT(cb, fmla, 10)THROUGHPUT(cb, fmla, 5)THROUGHPUT(cb, fmla, 2)THROUGHPUT(cb, fmla, 1)在这个例子中,分别对不进行循环展开和以粒度为 2、5、10、20 的循环展开的fmla计算进行测试,结果如下:

| UNROLL_NUM:1 | UNROLL_NUM:2 | UNROLL_NUM:5 | UNROLL_NUM:10 | UNROLL_NUM:20 |

|---|---|---|---|---|

| Interlock_FPU : 0.49998 | Interlock_FPU : 0.25727 | Interlock_FPU : 0.02236 | Interlock_FPU : 0.02519 | Interlock_FPU : 0.02681 |

| Metric_GFLOPs_Use : 3.98409 | Metric_GFLOPs_Use : 7.88556 | Metric_GFLOPs_Use : 12.97569 | Metric_GFLOPs_Use : 14.12275 | Metric_GFLOPs_Use : 14.74720 |

通过这个简单的例子我们可以看到,随着循环展开粒度的增加,Interlock_FPU 会逐渐降低,并逐渐趋于稳定。这是因为没有循环展开或循环展开特别小的时候,上一次循环还没有执行完成,下一次循环又要读取相同的寄存器,进而造成寄存器依赖。要消除寄存器依赖,首先要保证循环体中不同条指令使用不同的寄存器,并且尽量保证循环体内指令的条数大于该指令的 latency 和该指令的 throughput 的乘积。以本文在 a55 平台测试 fmla 向量计算为例,fmla的 latency 为 4 个 cycle,并且 a55 处理器后端只有一个 port 可以执行 fmla 向量计算,也即 fmla 的 throughput 为 1,所以要求循环体 fmla 指令数大于 4 * 1 才可以解除寄存器依赖,这也符合上述试验结果的变化情况。

理解上面信息后,我们考虑在 Naive 版本上进行循环展开,并依据 Naive 版本 Metric_Neon_Port_Util 为 0,同时施加 SIMD 优化。具体做法是,先对前面的行列采用 812 展开,对剩余的列采用 84 展开,再对剩余的行先采用 412 展开,最后用 44 展开,期间配合 ARM NEON 指令进行向量化操作。

这里选择 8*12 是为了更充分的利用寄存器资源,是因为 ARM A55 上面有 32 个128 bit 向量寄存器,以及考虑到本文最后 matmul 汇编版本的最内层实现大体如下(注意这里使用的外积计算矩阵乘,具体参见外积算矩阵乘):

- 从 A 矩阵读 8 个 float 到 2 个向量寄存器,此时应该是 8 行里面每行的第一个数。

- 从 B 矩阵读 12个float 到 3 个向量寄存器,应该是 12 列里每列的第一个数。

- 用fmla指令,让 B 的每个 float 分别乘以A的两个向量寄存器,产生 24 个向量结果,也全部存储在寄存器中( 24 个向量寄存器存储 8x12=96 个中间结果)。

采用 8*12 展开之后的代码结构如下:

void my_matmul_unroll(int m, int n, int k, float* a, int lda, float* b, int ldb, float* c, int ldc) { int i, j; for (i = 0; i + 8 <= m; i += 8) { for (j = 0; j + 12 <= n; j += 12) { AddDot8x12(k, &A(i, 0), lda, &B(0, j), ldb, &C(i, j), ldc); } for (; j < n; j += 4) { AddDot8x4(k, &A(i, 0), lda, &B(0, j), ldb, &C(i, j), ldc); } } if (i != m) { for (j = 0; j + 12 <= n; j += 12) { AddDot4x12(k, &A(i, 0), lda, &B(0, j), ldb, &C(i, j), ldc); } for (; j < n; j += 4) { AddDot4x4(k, &A(i, 0), lda, &B(0, j), ldb, &C(i, j), ldc); } }}关于循环展开,可以用一个图来直观地理解,这里 mr=8,nr=12,我们每次用 A 矩阵的 8 * K 的小块和 B 矩阵的 K * 12 小块来计算 C 的一个 8 * 12 小块:

用 mperf 分析 unroll 版本的 matmul 实现,具体数据见[ Unroll_mperf ] (https://www.megengine.org.cn/blog/mperf2#:~:text=Metric_GFLOPs_Use %3A 0.30557-,Unroll_mperf,-M%3DN%3DK)

对比 M,N,K 较小时(注: 在优化寄存器和 FPU 单元利用率的时候可以把问题规模先限制得比较小,减少访存相关 issue 的干扰),Unroll 版本与 Naive 版本的 Interlock_FPU、Metric_Neon_Port_Util 和 GFLOPS:

| loop | unroll | loop | unroll | loop | unroll |

|---|---|---|---|---|---|

| M=N=K=100 | M=N=K=100 | M=N=K=200 | M=N=K=200 | M=N=K=300 | M=N=K=300 |

| Interlock_FPU : 0.41489 | Interlock_FPU : 0.11604 | Interlock_FPU : 0.39121 | Interlock_FPU : 0.11293 | Interlock_FPU : 0.34547 | Interlock_FPU : 0.11227 |

| Metric_Neon_Port_Util : 0.00000 | Metric_Neon_Port_Util : 0.35740 | Metric_Neon_Port_Util : 0.00000 | Metric_Neon_Port_Util : 0.34510 | Metric_Neon_Port_Util : 0.00000 | Metric_Neon_Port_Util : 0.33232 |

| Metric_GFLOPs_Use : 0.36511 | Metric_GFLOPs_Use : 5.73161 | Metric_GFLOPs_Use : 0.34685 | Metric_GFLOPs_Use : 5.50208 | Metric_GFLOPs_Use : 0.30557 | Metric_GFLOPs_Use : 5.24582 |

可以看到循环展开后可以看到 Interlock_FPU 占比下降明显,同时 Metric_Neon_Port_Util 明显上升,而 GFLOPS 指标有了数量级的提高,说明充分利用寄存器资源和提高 FPU 利用率有效提高了程序性能。

访存优化——分块和 PACK

上图是 Unroll 版本与 Naive 版本在不同矩阵尺寸下的性能对比,可以看到循环展开在矩阵尺寸比较小的情况下,性能提升还是很明显的,但是随着矩阵尺寸增大 unroll 的效果迅速下降。所以现在我们将注意力转移到,如何解决矩阵尺寸增大 GFLOPS 下降的问题。通过分析上节链接的 unroll 版本的 mperf 数据,可以看到,随着矩阵尺寸变大到一定程度,Memory_Bound 占比逐渐接近 50%,替代之前的 Interlock_FPU 成为新的性能瓶颈。而 Memory_Bound 占比高主要是 Load_Cache 造成的,这就指明了我们接下来需要进行访存相关的优化。

分块

之所以矩阵尺寸增加,unroll 版本的性能会下降,主要原因就是数据无法全部驻留在 Cache 中,导致数据频繁地在 Cache 和主存之间换入换出,而处理器对主存的访问是非常昂贵的。为了减少对主存的重复访存,首先我们能想到的就是分块( Unroll 版本中提到的分块是内层分块,目的是优化寄存器和 FPU 的利用率,请注意区分),将分块之后的数据保存在 Cache 中,尽量使处理器发起的访存操作都能命中 cache 中的数据。

这里我们选择对 N,K 维分别进行 Nr 和 Kr 粒度的分块,结合循环展开部分的逻辑,整体的分块方式即为:外层选取 A 矩阵的 MKr 小块和 B 矩阵的 KrNr 小块,内层再对这两个小块分别进行 mr 行和 nr 列的划分,所以最终内层每次计算 mrKr 的 A 小块和 Krnr 的 B 小块,得到 C 矩阵 mr*nr 小块的部分中间结果。

关于如何确定 Nr 和 Kr 的大小,我们的目标就是使得计算时需要用到的分块可以根据访存频繁的程度保存在 CPU 的各级存储中,原则就是访问越频繁的分块存储在速度越快的存储上,以及保证优先用满速度快的存储资源之后再下溢。针对 matmul, 具体约束条件设定为:

- 将重复访存率最高的 mr*nr 大小的 C 小块保存在访存速度最快的寄存器上(unroll 版本就是这样假设的)。

- 将下图中红色部分(包括计算完一个 mrNr 的 C 行块需要重复访问次数最多的 mrKr 的 A 行块,内层一次计算迭代需要用到的 Kr*nr 大小的 B 列块)都保存在 L1 中。

- 由于计算完每一个 mrNr 的 C 行块,都需要重复遍历一次整个 KrNr 大小的 B 块,因此希望将 KrNr 大小的 B 块存放在 L2 中,使得每次读取 Krnr 的 B 列块的时候,都是从 L2 中读取。

依据上面的分配策略,并结合 CPU 中的各级存储资源(寄存器数量,L1D 和 L2 )的尺寸,便可以确定最佳的 Nr,Kr 取值:

- 可以根据 CPU 处理器的寄存器数量得到 mr 和 nr 的具体大小,寄存器容量>mr*nr (unroll 版本就是遵循这个约束条件取的 mr=8,nr=12)

- 根据 L1D Cache 的大小结合 mr 和 nr 计算出 Kr,Kr=L1D/(mr+nr)

- 再根据 L2 的大小计算出 B 矩阵中的 Nr,Nr=(L2-L1D)/Kr

在 ARM A55 上,最终得到的 Nr 为 252,Kr 为 256。注意:这里计算得到 Nr 为 256,但是由于我们选择 nr 为 12,因此为了避免不必要的余数处理,选择 Nr 为 12 的倍数简化问题。

Kr/Nr 分块的代码逻辑如下:

#define kc 256#define nc 252void my_mamtmul_block(int m, int n, int k, float *a, int lda, float *b, int ldb, float *c, int ldc) { int j, p, pb, ib; for (p = 0; p < k; p += kc) { pb = min(k - p, kc); for (j = 0; j < n; j += nc) { ib = min(n - j, nc); InnerKernel(m, ib, pb, &A(0, p), lda, &B(p, j), ldb, &C(0, j), ldc); } }}添加 Kr/Nr 分块后的 mperf 性能数据见 Block_mperf

对比 Kr/Nr 分块前后以下变化明显的数据:

| unroll | block | unroll | block |

|---|---|---|---|

| M=N=K=700 | M=N=K=700 | M=N=K=900 | M=N=K=900 |

| Memory_Bound : 0.31008 | Memory_Bound : 0.23551 | Memory_Bound : 0.48435 | Memory_Bound : 0.25875 |

| Load_Bound : 0.31003 | Load_Bound : 0.23547 | Load_Bound : 0.48433 | Load_Bound : 0.25870 |

| Load_DTLB : 0.01087 | Load_DTLB : 0.01252 | Load_DTLB : 0.01226 | Load_DTLB : 0.02023 |

| Load_Cache : 0.30802 | Load_Cache : 0.21025 | Load_Cache : 0.45685 | Load_Cache : 0.23244 |

| Store_Bound : 0.00005 | Store_Bound : 0.00004 | Store_Bound : 0.00002 | Store_Bound : 0.00005 |

| Store_TLB : 0.00003 | Store_TLB : 0.00010 | Store_TLB : 0.00002 | Store_TLB : 0.00004 |

| Store_Buffer : 0.00001 | Store_Buffer : 0.00001 | Store_Buffer : 0.00000 | Store_Buffer : 0.00001 |

| Metric_L1D_Miss_Ratio : 0.03458 | Metric_L1D_Miss_Ratio : 0.01878 | Metric_L1D_Miss_Ratio : 0.03515 | Metric_L1D_Miss_Ratio : 0.02113 |

| Metric_L1D_RD_Miss_Ratio : 0.03581 | Metric_L1D_RD_Miss_Ratio : 0.02030 | Metric_L1D_RD_Miss_Ratio : 0.03639 | Metric_L1D_RD_Miss_Ratio : 0.02284 |

| Metric_L1D_WR_Miss_Ratio : 0.00379 | Metric_L1D_WR_Miss_Ratio : 0.00169 | Metric_L1D_WR_Miss_Ratio : 0.00390 | Metric_L1D_WR_Miss_Ratio : 0.00189 |

| Metric_L2D_Miss_Ratio : 0.15673 | Metric_L2D_Miss_Ratio : 0.26215 | Metric_L2D_Miss_Ratio : 0.18801 | Metric_L2D_Miss_Ratio : 0.23144 |

| Metric_L2D_RD_Miss_Ratio : 0.31396 | Metric_L2D_RD_Miss_Ratio : 0.52642 | Metric_L2D_RD_Miss_Ratio : 0.37706 | Metric_L2D_RD_Miss_Ratio : 0.46396 |

| Metric_L2D_WR_Miss_Ratio : 0.00000 | Metric_L2D_WR_Miss_Ratio : 0.00000 | Metric_L2D_WR_Miss_Ratio : 0.00000 | Metric_L2D_WR_Miss_Ratio : 0.00000 |

| Metric_L3D_Miss_Ratio : 0.18870 | Metric_L3D_Miss_Ratio : 0.05405 | Metric_L3D_Miss_Ratio : 0.23623 | Metric_L3D_Miss_Ratio : 0.05183 |

| Metric_L3D_RD_Miss_Ratio : 0.38055 | Metric_L3D_RD_Miss_Ratio : 0.10890 | Metric_L3D_RD_Miss_Ratio : 0.47494 | Metric_L3D_RD_Miss_Ratio : 0.10425 |

| Metric_Load_Port_Util : 0.12046 | Metric_Load_Port_Util : 0.13779 | Metric_Load_Port_Util : 0.09069 | Metric_Load_Port_Util : 0.13191 |

| Metric_Store_Port_Util : 0.07090 | Metric_Store_Port_Util : 0.08126 | Metric_Store_Port_Util : 0.05370 | Metric_Store_Port_Util : 0.07829 |

| Metric_GFLOPs_Use : 3.95044 | Metric_GFLOPs_Use : 4.53463 | Metric_GFLOPs_Use : 3.03964 | Metric_GFLOPs_Use : 4.37174 |

Kr/Nr 分块后可以看到在矩阵较大时进行快速矩阵乘法,GFLOPS 确实上升不少,Load_Cache 和 Metric_L3D_RD_Miss_Ratio 等均有明显下降。这说明 Kr/Nr分块确实大幅减少了对 latency 非常大的系统主存的访问,优化了程序的访存性能。

数据 PACK

分析 Kr/Nr 分块后测得的 mperf 数据,可以看到随着矩阵尺寸变大,性能也能保持相对稳定,没有明显下降。但是此时 mperf 拿到的 TMA 指标显示, Backend_Bound 中的 Memory_Bound 占比依旧很高,性能瓶颈还是停留在访存部分。

进一步思考,在计算 mrnr 大小的 C 小块的时候,每一次迭代都需要读取 A 矩阵 mr1 的数据,而本文测试的矩阵数据都是行主序,即不同行相同列的数据是内存不连续的,访存不连续就意味着对 Cache 不友好。同样在不同次迭代中,需要读取矩阵 B 中不同行的 1*nr 小块的数据,自然也存在数据读取不连续的情况。考虑到在分块计算 matmul 的逻辑下,A 的所有行块和 B 中的所有列块将被读取多次,因此可以通过对 A 和 B 提前进行数据 PACK,这样只在第一次 PACK 时候对 Cache 不友好,而后面计算的时候多次访问数据均为连续访存,因此收益巨大。下图说明了对 A/B 矩阵分别 PACK 的过程:

void InnerKernel(int m, int n, int k, float* a, int lda, float* b, int ldb, float* c, int ldc) { int i, j; float packedA[m * k]; float packedB[k * n]; for (i = 0; i + 8 <= m; i += 8) { PackMatrixA_8(k, &A(i, 0), lda, packedA + i * k); for (j = 0; j + 12 <= n; j += 12) { if (0 == i) { PackMatrixB_12(k, &B(0, j), ldb, packedB + j * k); } AddDot8x12(k, packedA + i * k, k, packedB + j * k, 12, &C(i, j), ldc); } for (; j < n; j += 4) { if (0 == i) { PackMatrixB_4(k, &B(0, j), ldb, packedB + j * k); } AddDot8x4(k, packedA + i * k, k, packedB + j * k, 12, &C(i, j), ldc); } } if (i != m) { PackMatrixA_4(k, &A(i, 0), lda, packedA + i * k); for (j = 0; j + 12 <= n; j += 12) { AddDot4x12(k, packedA + i * k, k, packedB + j * k, 12, &C(i, j), ldc); } for (; j < n; j += 4) { AddDot4x4(k, packedA + i * k, k, packedB + j * k, 12, &C(i, j), ldc); } }}PACK 后的 mperf 性能数据见 Pack_mperf

对比 PACK 前后的数据:

| block | pack | block | pack | block | pack | block | pack | block | pack | block | pack |

|---|---|---|---|---|---|---|---|---|---|---|---|

| M=N=K=100 | M=N=K=100 | M=N=K=200 | M=N=K=200 | M=N=K=300 | M=N=K=300 | M=N=K=500 | M=N=K=500 | M=N=K=700 | M=N=K=700 | M=N=K=900 | M=N=K=900 |

| Load_Cache:0.04850 | Load_Cache:0.03037 | Load_Cache:0.05591 | Load_Cache:0.01925 | Load_Cache:0.09417 | Load_Cache:0.05596 | Load_Cache:0.16088 | Load_Cache:0.11704 | Load_Cache:0.20015 | Load_Cache:0.20065 | Load_Cache:0.23572 | Load_Cache:0.22885 |

| Interlock_FPU:0.09043 | Interlock_FPU:0.34918 | Interlock_FPU:0.08863 | Interlock_FPU:0.37332 | Interlock_FPU:0.08732 | Interlock_FPU:0.36597 | Interlock_FPU:0.07988 | Interlock_FPU:0.34384 | Interlock_FPU:0.07642 | Interlock_FPU:0.31200 | Interlock_FPU:0.07156 | Interlock_FPU:0.30176 |

| Metric_L1D_TLB_Miss_Ratio:0.00090 | Metric_L1D_TLB_Miss_Ratio:0.00224 | Metric_L1D_TLB_Miss_Ratio:0.00483 | Metric_L1D_TLB_Miss_Ratio:0.00235 | Metric_L1D_TLB_Miss_Ratio:0.00685 | Metric_L1D_TLB_Miss_Ratio:0.00294 | Metric_L1D_TLB_Miss_Ratio:0.01143 | Metric_L1D_TLB_Miss_Ratio:0.00328 | Metric_L1D_TLB_Miss_Ratio:0.01573 | Metric_L1D_TLB_Miss_Ratio:0.00413 | Metric_L1D_TLB_Miss_Ratio:0.01915 | Metric_L1D_TLB_Miss_Ratio:0.00511 |

| Metric_L2_TLB_Miss_Ratio:0.00000 | Metric_L2_TLB_Miss_Ratio:0.00000 | Metric_L2_TLB_Miss_Ratio:0.00001 | Metric_L2_TLB_Miss_Ratio:0.00013 | Metric_L2_TLB_Miss_Ratio:0.00001 | Metric_L2_TLB_Miss_Ratio:0.00072 | Metric_L2_TLB_Miss_Ratio:0.00048 | Metric_L2_TLB_Miss_Ratio:0.01302 | Metric_L2_TLB_Miss_Ratio:0.02578 | Metric_L2_TLB_Miss_Ratio:0.07241 | Metric_L2_TLB_Miss_Ratio:0.06266 | Metric_L2_TLB_Miss_Ratio:0.26738 |

| L2D_TLB_REFILL0.000000 | L2D_TLB_REFILL0.000000 | L2D_TLB_REFILL0.200000 | L2D_TLB_REFILL0.700000 | L2D_TLB_REFILL1.200000 | L2D_TLB_REFILL10.800000 | L2D_TLB_REFILL358.600006 | L2D_TLB_REFILL956.500000 | L2D_TLB_REFILL72607.601562 | L2D_TLB_REFILL16910.800781 | L2D_TLB_REFILL460042.187500 | L2D_TLB_REFILL157443.500000 |

| L2D_TLB910.400024 | L2D_TLB822.400024 | L2D_TLB23194.500000 | L2D_TLB5456.500000 | L2D_TLB97020.296875 | L2D_TLB15094.200195 | L2D_TLB744285.812500 | L2D_TLB73438.000000 | L2D_TLB2816898.500000 | L2D_TLB233527.500000 | L2D_TLB7341533.500000 | L2D_TLB588828.312500 |

| Metric_GFLOPs_Use:6.34394 | Metric_GFLOPs_Use:7.00634 | Metric_GFLOPs_Use:6.24761 | Metric_GFLOPs_Use:7.27444 | Metric_GFLOPs_Use:5.86449 | Metric_GFLOPs_Use:6.94621 | Metric_GFLOPs_Use:5.53592 | Metric_GFLOPs_Use:6.66007 | Metric_GFLOPs_Use:5.10062 | Metric_GFLOPs_Use:5.91676 | Metric_GFLOPs_Use:4.89490 | Metric_GFLOPs_Use:5.65741 |

可以看到进行 PACK 优化后 GFLOPS 又有一定幅度的增长。此时可以观察到 L1D_TLB_Miss_Ratio 有所降低,并且在 M=N=K >= 700 时L2D_TLB_REFILL明显降低,说明 PACK 确实可以通过减少缺页的发生,减少 TLB miss,从而提升性能。

pipeline 优化——嵌入汇编

分析 PACK 之后的 mperf 数据,可以发现 Backend_Bound 占比 40% 以上,其中 Core_Bound 类别下的 Interlock_FPU 再次成为性能瓶颈。回想 unroll 版本减少 Interlock_FPU 的思路,是通过循环展开给编译器更大的优化空间,让编译器充分利用寄存器来减少流水线依赖,但编译器也是有局限的。一般来说,编译器考虑到通用性,是很难生成针对特定处理器架构特点的最优汇编实现的( ARM in-order 架构的小核上更是如此)。因此下一步的想法就是优化编译器生成的汇编,通过把内层计算逻辑替换为嵌入式汇编,依据架构特性调整指令选择和指令排布,进一步减少 pipeline 上的依赖和冲突,从而达成降低 Interlock_FPU 的目的。

首先,我们对比了 PACK 版本的 mperf 数据中的 FPU_util 和纯算力测试情况下的 FPU_util,发现 PACK 版本的 FPU_util 相对低了很多。也就是说,PACK 版本的 matmul 对处理器 SIMD 单元的利用率还是有一定提升空间的(下这个判断的一个前提也是考虑到前文已经对 matmul 访存部分优化得很充分了,并且考虑到内层循环中没有分支判断等复杂逻辑,只是比较存粹的访存和计算指令的 interleave。换句话说,汇编优化一般是留到最后进行的)。

其次,我们注意到编译器生成的汇编代码中,数据加载使用的是 ldq 指令(ldq 指的是 armv8 isa 中 128bit load 操作),但是结合上面 FPU_util 数值比理想情况低的观察(会关注 ldq 指令,是因为我们了解到 ARM A55 的访存能力弱,一个 cycle 最多 load 64bit,store 128bit),我们有理由怀疑 ldq 指令的选择可能会造成 pipeline stall。通过查询 ARM A55 trm 手册,我们发现 ldq 在 a55 上需要两个 cycle 才能 issue 出去,并且 ldq 跟 fmla 不能双发射(注: ARM A55 是双发射架构),这就证实了 ldq 会造成计算和访存指令无法双发射,并造成 Metric_FPU_util 数值的下降。进一步,我们发现 ldr,ldx,ins 三种指令都能与 fmla 双发射,且发射周期都是 1 个 cycle,而这三条指令可以组合出 ldq 等价的操作。因此,我们使用 ldr,ldx,ins 指令组合来替换 ldq 指令,就可以提高流水线的满载程度,进而提高性能。

我们用一个小的测试例子来进行验证: 考虑下面两段代码: 优化前,使用 ldq 指令加载数据,代码如下:

asm volatile( "fmla v1.4s, v1.4s, v1.s[0]\n" "ld1 {v0.4s}, [%[b_ptr]]\n" "fmla v2.4s, v2.4s, v2.s[0]\n" "ld1 {v7.4s}, [%[b_ptr]]\n" "fmla v3.4s, v3.4s, v3.s[0]\n" "fmla v4.4s, v4.4s, v4.s[0]\n" "fmla v5.4s, v5.4s, v5.s[0]\n" "fmla v6.4s, v6.4s, v6.s[0]\n" : [b_ptr] "+r"(b_ptr) : : "v0", "v1", "v2", "v3", "v4", "v5", "v6", "v7");优化后,将 ldq 拆分为 ldr,ldx,ins 指令加载数据,代码如下:

asm volatile( "fmla v1.4s, v1.4s, v1.s[0]\n" "ldr d0, [%[b_ptr]]\n" "fmla v2.4s, v2.4s, v2.s[0]\n" "ldr x0, [%[b_ptr], #8]\n" "fmla v3.4s, v3.4s, v3.s[0]\n" "ins v0.d[1], x0\n" "fmla v4.4s, v4.4s, v4.s[0]\n" "ldr d7, [%[b_ptr]]\n" "fmla v5.4s, v5.4s, v5.s[0]\n" "ldr x0, [%[b_ptr], #8]\n" "fmla v6.4s, v6.4s, v6.s[0]\n" "ins v7.d[1], x0\n" : [b_ptr] "+r"(b_ptr) : : "v0", "v1", "v2", "v3", "v4", "v5", "v6", "v7");我们对优化前和优化后的版本进行测试,对分析 mperf 拿到的数据,看到主要的变化为:

| ldq | ldr+ldr+ins |

|---|---|

| Metric_Load_Port_Util : 0.39650 | Metric_Load_Port_Util : 0.69312 |

| Metric_GFLOPs_Use : 5.00572 | Metric_GFLOPs_Use : 7.70664 |

可以看到Metric_Load_Port_Util 和 Metric_GFLOPs_Use 均提升明显,也就验证了前面的猜想。

因此,在嵌入的汇编代码中,我们应用上面提到的加载指令的替换,测得的 mperf 性能数据见:ASM_mperf

对比分析 PACK 和 ASM 两个版本的 mperf 数据,可以看到 Metric_Neon_Port_Util 和 Metric_Load_Port_Util 均显著上升。

| PACK | ASM | PACK | ASM | PACK | ASM | PACK | ASM | PACK | ASM |

|---|---|---|---|---|---|---|---|---|---|

| M=N=K=200 | M=N=K=200 | M=N=K=300 | M=N=K=300 | M=N=K=500 | M=N=K=500 | M=N=K=700 | M=N=K=700 | M=N=K=900 | M=N=K=900 |

| Bad_Speculation : 0.29156 | Bad_Speculation : 0.13931 | Bad_Speculation : 0.27964 | Bad_Speculation : 0.10896 | Bad_Speculation : 0.26751 | Bad_Speculation : 0.02394 | Bad_Speculation : 0.24406 | Bad_Speculation : 0.07470 | Bad_Speculation : 0.22907 | Bad_Speculation : 0.06565 |

| Branch_Mispredicts : 530.09998 | Branch_Mispredicts : 516.29999 | Branch_Mispredicts : 1718.09998 | Branch_Mispredicts : 1237.50000 | Branch_Mispredicts : 7551.70020 | Branch_Mispredicts : 6101.39990 | Branch_Mispredicts : 22910.50000 | Branch_Mispredicts : 17442.59961 | Branch_Mispredicts : 50927.00000 | Branch_Mispredicts : 37761.50000 |

| Load_Cache : 0.01824 | Load_Cache : 0.02975 | Load_Cache : 0.05483 | Load_Cache : 0.10898 | Load_Cache : 0.10329 | Load_Cache : 0.25344 | Load_Cache : 0.20224 | Load_Cache : 0.38846 | Load_Cache : 0.21719 | Load_Cache : 0.42574 |

| Interlock_FPU : 0.37414 | Interlock_FPU : 0.00000 | Interlock_FPU : 0.36819 | Interlock_FPU : 0.00000 | Interlock_FPU : 0.34176 | Interlock_FPU : 0.00000 | Interlock_FPU : 0.31210 | Interlock_FPU : 0.00000 | Interlock_FPU : 0.30707 | Interlock_FPU : 0.00000 |

| Retiring : 0.30317 | Retiring : 0.79307 | Retiring : 0.28769 | Retiring : 0.74938 | Retiring : 0.26564 | Retiring : 0.64852 | Retiring : 0.23871 | Retiring : 0.50446 | Retiring : 0.23278 | Retiring : 0.47370 |

| LD_Retiring : 0.04036 | LD_Retiring : 0.21852 | LD_Retiring : 0.03691 | LD_Retiring : 0.20725 | LD_Retiring : 0.03349 | LD_Retiring : 0.17772 | LD_Retiring : 0.02966 | LD_Retiring : 0.13824 | LD_Retiring : 0.02869 | LD_Retiring : 0.12980 |

| ST_Retiring : 0.00510 | ST_Retiring : 0.01946 | ST_Retiring : 0.00493 | ST_Retiring : 0.01859 | ST_Retiring : 0.00279 | ST_Retiring : 0.00998 | ST_Retiring : 0.00241 | ST_Retiring : 0.00750 | ST_Retiring : 0.00230 | ST_Retiring : 0.00690 |

| DP_Retiring : 0.02283 | DP_Retiring : 0.03734 | DP_Retiring : 0.02146 | DP_Retiring : 0.03561 | DP_Retiring : 0.01926 | DP_Retiring : 0.02792 | DP_Retiring : 0.01710 | DP_Retiring : 0.02162 | DP_Retiring : 0.01657 | DP_Retiring : 0.02026 |

| ASE_Retiring : 0.22917 | ASE_Retiring : 0.42233 | ASE_Retiring : 0.21917 | ASE_Retiring : 0.39544 | ASE_Retiring : 0.20533 | ASE_Retiring : 0.35224 | ASE_Retiring : 0.18532 | ASE_Retiring : 0.27398 | ASE_Retiring : 0.18116 | ASE_Retiring : 0.25727 |

| VFP_Retiring : 0.22917 | VFP_Retiring : 0.42233 | VFP_Retiring : 0.21917 | VFP_Retiring : 0.39544 | VFP_Retiring : 0.20533 | VFP_Retiring : 0.35224 | VFP_Retiring : 0.18532 | VFP_Retiring : 0.27398 | VFP_Retiring : 0.18116 | VFP_Retiring : 0.25727 |

| Metric_Load_Port_Util : 0.08072 | Metric_Load_Port_Util : 0.43704 | Metric_Load_Port_Util : 0.07381 | Metric_Load_Port_Util : 0.41450 | Metric_Load_Port_Util : 0.06698 | Metric_Load_Port_Util : 0.35545 | Metric_Load_Port_Util : 0.05932 | Metric_Load_Port_Util : 0.27647 | Metric_Load_Port_Util : 0.05737 | Metric_Load_Port_Util : 0.25961 |

| Metric_Neon_Port_Util : 0.45834 | Metric_Neon_Port_Util : 0.84466 | Metric_Neon_Port_Util : 0.43834 | Metric_Neon_Port_Util : 0.79088 | Metric_Neon_Port_Util : 0.41067 | Metric_Neon_Port_Util : 0.70447 | Metric_Neon_Port_Util : 0.37064 | Metric_Neon_Port_Util : 0.54795 | Metric_Neon_Port_Util : 0.36232 | Metric_Neon_Port_Util : 0.51453 |

| Metric_GFLOPs_Use : 7.27027 | Metric_GFLOPs_Use : 13.45224 | Metric_GFLOPs_Use : 6.96883 | Metric_GFLOPs_Use : 12.57732 | Metric_GFLOPs_Use : 6.63430 | Metric_GFLOPs_Use : 10.50762 | Metric_GFLOPs_Use : 5.88770 | Metric_GFLOPs_Use : 8.73145 | Metric_GFLOPs_Use : 5.75827 | Metric_GFLOPs_Use : 8.13339 |

注意到完成汇编优化后,在矩阵大小 M,N,K <= 300 时,GFLOPS 性能已经达到峰值算力的 90% 以上,基本上可以判定较小尺寸的情况下,matmul 在 ARM A55 平台上已经优化到位了。而当 M,N,K 比较大时,依旧有进一步的优化空间。但是考虑到本文的主要目的,是借助 matmul 优化来说明 mperf 可以给性能优化工作带来哪些助益,所以就不继续进一步的优化关工作了。

总结

本文以 ARM A55 平台上的矩阵乘优化为例,详细介绍了如何用 mperf 分析当前实现的性能表现,找到性能瓶颈,进而确定下一步的优化方向,如此反复迭代,最终取得了接近硬件性能峰值的性能表现。本文各个版本 matmul 的性能对比,见下图:

附录

mperf测试数据

这里贴了不同优化版本的 mperf 测试数据,每一个版本下的测试数据都包含两部分:一部分是非 Metric 前缀命名的,都是 TMA 范式下的指标;另一部分是 Metric 前缀命名的则是非 TMA 范式下,但是对性能优化有辅助作用的指标。这两类指标都是基于 PMU 原始 event 四则运算加工得到的,具体的计算公式请参见 ARM a55 tma 。

另,TMA 范式下的指标呈现多级展开的关系,由于当前 mperf 未提供可视化工具,请参考下图示意的层级关系进行对号入座。并且,请注意附录贴的 TMA 数值均为无量纲百分比。

Naive_mperf

| M=N=K=100 | M=N=K=200 | M=N=K=300 |

|---|---|---|

| Frontend_Bound : 0.00319 | Frontend_Bound : 0.00149 | Frontend_Bound : 0.00088 |

| Fetch_Latency : 0.00319 | Fetch_Latency : 0.00149 | Fetch_Latency : 0.00088 |

| ICache_Misses : 0.00004 | ICache_Misses : 0.00001 | ICache_Misses : 0.00001 |

| ITLB_Misses : 0.00000 | ITLB_Misses : 0.00001 | ITLB_Misses : 0.00000 |

| Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 |

| Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 |

| Bad_Speculation : 0.16147 | Bad_Speculation : 0.14928 | Bad_Speculation : 0.13111 |

| Branch_Mispredicts : 10112.59961 | Branch_Mispredicts : 40262.80078 | Branch_Mispredicts : 90512.79688 |

| Backend_Bound : 0.46695 | Backend_Bound : 0.50441 | Backend_Bound : 0.56425 |

| Memory_Bound : 0.04070 | Memory_Bound : 0.08765 | Memory_Bound : 0.18501 |

| Load_Bound : 0.04054 | Load_Bound : 0.08667 | Load_Bound : 0.18443 |

| Load_DTLB : 0.00002 | Load_DTLB : 0.03964 | Load_DTLB : 0.05109 |

| Load_Cache : 0.04006 | Load_Cache : 0.04649 | Load_Cache : 0.13333 |

| Store_Bound : 0.00016 | Store_Bound : 0.00098 | Store_Bound : 0.00058 |

| Store_TLB : 0.00000 | Store_TLB : 0.00098 | Store_TLB : 0.00058 |

| Store_Buffer : 0.00017 | Store_Buffer : 0.00000 | Store_Buffer : 0.00000 |

| Core_Bound : 0.42625 | Core_Bound : 0.41676 | Core_Bound : 0.37925 |

| Interlock_Bound : 0.41492 | Interlock_Bound : 0.39122 | Interlock_Bound : 0.34547 |

| Interlock_AGU : 0.00001 | Interlock_AGU : 0.00000 | Interlock_AGU : 0.00000 |

| Interlock_FPU : 0.41489 | Interlock_FPU : 0.39121 | Interlock_FPU : 0.34547 |

| Core_Bound_Others : 0.01133 | Core_Bound_Others : 0.02555 | Core_Bound_Others : 0.03378 |

| Retiring : 0.36839 | Retiring : 0.34483 | Retiring : 0.30376 |

| LD_Retiring : 0.10529 | LD_Retiring : 0.09854 | LD_Retiring : 0.08680 |

| ST_Retiring : 0.00055 | ST_Retiring : 0.00026 | ST_Retiring : 0.00015 |

| DP_Retiring : 0.10854 | DP_Retiring : 0.10006 | DP_Retiring : 0.08769 |

| ASE_Retiring : 0.00000 | ASE_Retiring : 0.00000 | ASE_Retiring : 0.00000 |

| VFP_Retiring : 0.10372 | VFP_Retiring : 0.09780 | VFP_Retiring : 0.08637 |

| PC_Write_Retiring : 0.05242 | PC_Write_Retiring : 0.04916 | PC_Write_Retiring : 0.04334 |

| BR_IMMED_Retiring : 0.05242 | BR_IMMED_Retiring : 0.04916 | BR_IMMED_Retiring : 0.04334 |

| BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 |

| BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 |

| Metric_L1D_Miss_Ratio : 0.05678 | Metric_L1D_Miss_Ratio : 0.02601 | Metric_L1D_Miss_Ratio : 0.06416 |

| Metric_L1D_RD_Miss_Ratio : 0.05673 | Metric_L1D_RD_Miss_Ratio : 0.02592 | Metric_L1D_RD_Miss_Ratio : 0.06405 |

| Metric_L1D_WR_Miss_Ratio : 0.17102 | Metric_L1D_WR_Miss_Ratio : 0.18698 | Metric_L1D_WR_Miss_Ratio : 0.33719 |

| Metric_L2D_Miss_Ratio : 0.00473 | Metric_L2D_Miss_Ratio : 0.14580 | Metric_L2D_Miss_Ratio : 0.23731 |

| Metric_L2D_RD_Miss_Ratio : 0.01038 | Metric_L2D_RD_Miss_Ratio : 0.29075 | Metric_L2D_RD_Miss_Ratio : 0.47490 |

| Metric_L2D_WR_Miss_Ratio : 0.00116 | Metric_L2D_WR_Miss_Ratio : 0.00014 | Metric_L2D_WR_Miss_Ratio : 0.00004 |

| Metric_L3D_Miss_Ratio : 0.00158 | Metric_L3D_Miss_Ratio : 0.00038 | Metric_L3D_Miss_Ratio : 0.00027 |

| Metric_L3D_RD_Miss_Ratio : 0.00399 | Metric_L3D_RD_Miss_Ratio : 0.00077 | Metric_L3D_RD_Miss_Ratio : 0.00054 |

| Metric_BR_Mispred_Ratio : 0.01000 | Metric_BR_Mispred_Ratio : 0.00501 | Metric_BR_Mispred_Ratio : 0.00334 |

| Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 |

| Metric_L1D_TLB_Miss_Ratio : 0.00007 | Metric_L1D_TLB_Miss_Ratio : 0.10279 | Metric_L1D_TLB_Miss_Ratio : 0.15008 |

| Metric_L2_TLB_Miss_Ratio : 0.00000 | Metric_L2_TLB_Miss_Ratio : 0.00000 | Metric_L2_TLB_Miss_Ratio : 0.00000 |

| Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 |

| Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 |

| Metric_Load_Port_Util : 0.21057 | Metric_Load_Port_Util : 0.19708 | Metric_Load_Port_Util : 0.17360 |

| Metric_Store_Port_Util : 0.00110 | Metric_Store_Port_Util : 0.00052 | Metric_Store_Port_Util : 0.00031 |

| Metric_Neon_Port_Util : 0.00000 | Metric_Neon_Port_Util : 0.00000 | Metric_Neon_Port_Util : 0.00000 |

| Metric_GFLOPs_Use : 0.36511 | Metric_GFLOPs_Use : 0.34685 | Metric_GFLOPs_Use : 0.30557 |

Unroll_mperf

| M=N=K=100 | M=N=K=200 | M=N=K=300 | M=N=K=500 | M=N=K=700 | M=N=K=900 |

|---|---|---|---|---|---|

| Frontend_Bound : 0.00074 | Frontend_Bound : 0.00016 | Frontend_Bound : 0.00010 | Frontend_Bound : 0.00007 | Frontend_Bound : 0.00008 | Frontend_Bound : 0.00006 |

| Fetch_Latency : 0.00074 | Fetch_Latency : 0.00016 | Fetch_Latency : 0.00010 | Fetch_Latency : 0.00007 | Fetch_Latency : 0.00008 | Fetch_Latency : 0.00006 |

| ICache_Misses : 0.00034 | ICache_Misses : 0.00004 | ICache_Misses : 0.00003 | ICache_Misses : 0.00003 | ICache_Misses : 0.00004 | ICache_Misses : 0.00004 |

| ITLB_Misses : 0.00000 | ITLB_Misses : 0.00000 | ITLB_Misses : 0.00000 | ITLB_Misses : 0.00004 | ITLB_Misses : 0.00001 | ITLB_Misses : 0.00001 |

| Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 |

| Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 |

| Bad_Speculation : 0.47808 | Bad_Speculation : 0.46884 | Bad_Speculation : 0.44958 | Bad_Speculation : 0.43876 | Bad_Speculation : 0.34968 | Bad_Speculation : 0.27817 |

| Branch_Mispredicts : 134.60001 | Branch_Mispredicts : 472.39999 | Branch_Mispredicts : 1017.79999 | Branch_Mispredicts : 2919.89990 | Branch_Mispredicts : 5817.79980 | Branch_Mispredicts : 10082.20020 |

| Backend_Bound : 0.18936 | Backend_Bound : 0.20947 | Backend_Bound : 0.24190 | Backend_Bound : 0.26918 | Backend_Bound : 0.41795 | Backend_Bound : 0.54684 |

| Memory_Bound : 0.04723 | Memory_Bound : 0.07794 | Memory_Bound : 0.10863 | Memory_Bound : 0.14413 | Memory_Bound : 0.31008 | Memory_Bound : 0.48435 |

| Load_Bound : 0.04660 | Load_Bound : 0.07781 | Load_Bound : 0.10861 | Load_Bound : 0.14411 | Load_Bound : 0.31003 | Load_Bound : 0.48433 |

| Load_DTLB : 0.00056 | Load_DTLB : 0.00293 | Load_DTLB : 0.00382 | Load_DTLB : 0.00629 | Load_DTLB : 0.01087 | Load_DTLB : 0.01226 |

| Load_Cache : 0.04502 | Load_Cache : 0.06666 | Load_Cache : 0.09210 | Load_Cache : 0.12851 | Load_Cache : 0.30802 | Load_Cache : 0.45685 |

| Store_Bound : 0.00063 | Store_Bound : 0.00013 | Store_Bound : 0.00002 | Store_Bound : 0.00002 | Store_Bound : 0.00005 | Store_Bound : 0.00002 |

| Store_TLB : 0.00001 | Store_TLB : 0.00001 | Store_TLB : 0.00001 | Store_TLB : 0.00001 | Store_TLB : 0.00003 | Store_TLB : 0.00002 |

| Store_Buffer : 0.00051 | Store_Buffer : 0.00011 | Store_Buffer : 0.00001 | Store_Buffer : 0.00001 | Store_Buffer : 0.00001 | Store_Buffer : 0.00000 |

| Core_Bound : 0.14213 | Core_Bound : 0.13153 | Core_Bound : 0.13327 | Core_Bound : 0.12505 | Core_Bound : 0.10787 | Core_Bound : 0.06249 |

| Interlock_Bound : 0.11653 | Interlock_Bound : 0.11316 | Interlock_Bound : 0.11241 | Interlock_Bound : 0.10508 | Interlock_Bound : 0.08437 | Interlock_Bound : 0.06386 |

| Interlock_AGU : 0.00033 | Interlock_AGU : 0.00016 | Interlock_AGU : 0.00010 | Interlock_AGU : 0.00006 | Interlock_AGU : 0.00003 | Interlock_AGU : 0.00002 |

| Interlock_FPU : 0.11604 | Interlock_FPU : 0.11293 | Interlock_FPU : 0.11227 | Interlock_FPU : 0.10500 | Interlock_FPU : 0.08432 | Interlock_FPU : 0.06384 |

| Core_Bound_Others : 0.02560 | Core_Bound_Others : 0.01837 | Core_Bound_Others : 0.02086 | Core_Bound_Others : 0.01997 | Core_Bound_Others : 0.02350 | Core_Bound_Others : -0.00137 |

| Retiring : 0.33182 | Retiring : 0.32153 | Retiring : 0.30842 | Retiring : 0.29199 | Retiring : 0.23229 | Retiring : 0.17493 |

| LD_Retiring : 0.08541 | LD_Retiring : 0.08371 | LD_Retiring : 0.07969 | LD_Retiring : 0.07575 | LD_Retiring : 0.06023 | LD_Retiring : 0.04534 |

| ST_Retiring : 0.04820 | ST_Retiring : 0.04789 | ST_Retiring : 0.04711 | ST_Retiring : 0.04411 | ST_Retiring : 0.03545 | ST_Retiring : 0.02685 |

| DP_Retiring : 0.01584 | DP_Retiring : 0.01401 | DP_Retiring : 0.01244 | DP_Retiring : 0.01195 | DP_Retiring : 0.00923 | DP_Retiring : 0.00684 |

| ASE_Retiring : 0.17870 | ASE_Retiring : 0.17255 | ASE_Retiring : 0.16616 | ASE_Retiring : 0.15724 | ASE_Retiring : 0.12510 | ASE_Retiring : 0.09421 |

| VFP_Retiring : 0.17870 | VFP_Retiring : 0.17255 | VFP_Retiring : 0.16616 | VFP_Retiring : 0.15724 | VFP_Retiring : 0.12510 | VFP_Retiring : 0.09421 |

| PC_Write_Retiring : 0.00395 | PC_Write_Retiring : 0.00350 | PC_Write_Retiring : 0.00310 | PC_Write_Retiring : 0.00298 | PC_Write_Retiring : 0.00231 | PC_Write_Retiring : 0.00171 |

| BR_IMMED_Retiring : 0.00394 | BR_IMMED_Retiring : 0.00350 | BR_IMMED_Retiring : 0.00310 | BR_IMMED_Retiring : 0.00298 | BR_IMMED_Retiring : 0.00231 | BR_IMMED_Retiring : 0.00171 |

| BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 |

| BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 |

| Metric_L1D_Miss_Ratio : 0.01625 | Metric_L1D_Miss_Ratio : 0.01791 | Metric_L1D_Miss_Ratio : 0.02479 | Metric_L1D_Miss_Ratio : 0.03246 | Metric_L1D_Miss_Ratio : 0.03458 | Metric_L1D_Miss_Ratio : 0.03515 |

| Metric_L1D_RD_Miss_Ratio : 0.01692 | Metric_L1D_RD_Miss_Ratio : 0.01863 | Metric_L1D_RD_Miss_Ratio : 0.02567 | Metric_L1D_RD_Miss_Ratio : 0.03369 | Metric_L1D_RD_Miss_Ratio : 0.03581 | Metric_L1D_RD_Miss_Ratio : 0.03639 |

| Metric_L1D_WR_Miss_Ratio : 0.00264 | Metric_L1D_WR_Miss_Ratio : 0.00239 | Metric_L1D_WR_Miss_Ratio : 0.00307 | Metric_L1D_WR_Miss_Ratio : 0.00338 | Metric_L1D_WR_Miss_Ratio : 0.00379 | Metric_L1D_WR_Miss_Ratio : 0.00390 |

| Metric_L2D_Miss_Ratio : 0.02740 | Metric_L2D_Miss_Ratio : 0.19737 | Metric_L2D_Miss_Ratio : 0.19336 | Metric_L2D_Miss_Ratio : 0.14853 | Metric_L2D_Miss_Ratio : 0.15673 | Metric_L2D_Miss_Ratio : 0.18801 |

| Metric_L2D_RD_Miss_Ratio : 0.05446 | Metric_L2D_RD_Miss_Ratio : 0.39807 | Metric_L2D_RD_Miss_Ratio : 0.38924 | Metric_L2D_RD_Miss_Ratio : 0.29803 | Metric_L2D_RD_Miss_Ratio : 0.31396 | Metric_L2D_RD_Miss_Ratio : 0.37706 |

| Metric_L2D_WR_Miss_Ratio : 0.00004 | Metric_L2D_WR_Miss_Ratio : 0.00000 | Metric_L2D_WR_Miss_Ratio : 0.00000 | Metric_L2D_WR_Miss_Ratio : 0.00000 | Metric_L2D_WR_Miss_Ratio : 0.00000 | Metric_L2D_WR_Miss_Ratio : 0.00000 |

| Metric_L3D_Miss_Ratio : 0.00000 | Metric_L3D_Miss_Ratio : 0.00010 | Metric_L3D_Miss_Ratio : 0.00160 | Metric_L3D_Miss_Ratio : 0.02646 | Metric_L3D_Miss_Ratio : 0.18870 | Metric_L3D_Miss_Ratio : 0.23623 |

| Metric_L3D_RD_Miss_Ratio : 0.00000 | Metric_L3D_RD_Miss_Ratio : 0.00020 | Metric_L3D_RD_Miss_Ratio : 0.00325 | Metric_L3D_RD_Miss_Ratio : 0.05356 | Metric_L3D_RD_Miss_Ratio : 0.38055 | Metric_L3D_RD_Miss_Ratio : 0.47494 |

| Metric_BR_Mispred_Ratio : 0.01048 | Metric_BR_Mispred_Ratio : 0.00500 | Metric_BR_Mispred_Ratio : 0.00346 | Metric_BR_Mispred_Ratio : 0.00211 | Metric_BR_Mispred_Ratio : 0.00158 | Metric_BR_Mispred_Ratio : 0.00131 |

| Metric_L1I_TLB_Miss_Ratio : 0.00001 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 |

| Metric_L1D_TLB_Miss_Ratio : 0.00087 | Metric_L1D_TLB_Miss_Ratio : 0.00432 | Metric_L1D_TLB_Miss_Ratio : 0.00584 | Metric_L1D_TLB_Miss_Ratio : 0.00984 | Metric_L1D_TLB_Miss_Ratio : 0.01323 | Metric_L1D_TLB_Miss_Ratio : 0.01621 |

| Metric_L2_TLB_Miss_Ratio : 0.00000 | Metric_L2_TLB_Miss_Ratio : 0.00001 | Metric_L2_TLB_Miss_Ratio : 0.00005 | Metric_L2_TLB_Miss_Ratio : 0.00035 | Metric_L2_TLB_Miss_Ratio : 0.02917 | Metric_L2_TLB_Miss_Ratio : 0.04803 |

| Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 |

| Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00039 | Metric_DTLB_Table_Walk_Ratio : 0.00078 |

| Metric_Load_Port_Util : 0.17082 | Metric_Load_Port_Util : 0.16742 | Metric_Load_Port_Util : 0.15939 | Metric_Load_Port_Util : 0.15151 | Metric_Load_Port_Util : 0.12046 | Metric_Load_Port_Util : 0.09069 |

| Metric_Store_Port_Util : 0.09640 | Metric_Store_Port_Util : 0.09578 | Metric_Store_Port_Util : 0.09422 | Metric_Store_Port_Util : 0.08822 | Metric_Store_Port_Util : 0.07090 | Metric_Store_Port_Util : 0.05370 |

| Metric_Neon_Port_Util : 0.35740 | Metric_Neon_Port_Util : 0.34510 | Metric_Neon_Port_Util : 0.33232 | Metric_Neon_Port_Util : 0.31449 | Metric_Neon_Port_Util : 0.25020 | Metric_Neon_Port_Util : 0.18842 |

| Metric_GFLOPs_Use : 5.73161 | Metric_GFLOPs_Use : 5.50208 | Metric_GFLOPs_Use : 5.24582 | Metric_GFLOPs_Use : 4.97877 | Metric_GFLOPs_Use : 3.95044 | Metric_GFLOPs_Use : 3.03964 |

Block_mperf

| M=N=K=100 | M=N=K=200 | M=N=K=300 | M=N=K=500 | M=N=K=700 | M=N=K=900 |

|---|---|---|---|---|---|

| Frontend_Bound : 0.00050 | Frontend_Bound : 0.00014 | Frontend_Bound : 0.00013 | Frontend_Bound : 0.00013 | Frontend_Bound : 0.00016 | Frontend_Bound : 0.00014 |

| Fetch_Latency : 0.00050 | Fetch_Latency : 0.00014 | Fetch_Latency : 0.00013 | Fetch_Latency : 0.00013 | Fetch_Latency : 0.00016 | Fetch_Latency : 0.00014 |

| ICache_Misses : 0.00028 | ICache_Misses : 0.00004 | ICache_Misses : 0.00003 | ICache_Misses : 0.00005 | ICache_Misses : 0.00004 | ICache_Misses : 0.00003 |

| ITLB_Misses : 0.00001 | ITLB_Misses : 0.00000 | ITLB_Misses : 0.00000 | ITLB_Misses : 0.00004 | ITLB_Misses : 0.00002 | ITLB_Misses : 0.00001 |

| Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 |

| Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 |

| Bad_Speculation : 0.48119 | Bad_Speculation : 0.46947 | Bad_Speculation : 0.46177 | Bad_Speculation : 0.42173 | Bad_Speculation : 0.39518 | Bad_Speculation : 0.37718 |

| Branch_Mispredicts : 134.60001 | Branch_Mispredicts : 471.60001 | Branch_Mispredicts : 1535.69995 | Branch_Mispredicts : 7051.50000 | Branch_Mispredicts : 20853.69922 | Branch_Mispredicts : 46702.60156 |

| Backend_Bound : 0.18770 | Backend_Bound : 0.20837 | Backend_Bound : 0.22868 | Backend_Bound : 0.28475 | Backend_Bound : 0.33877 | Backend_Bound : 0.36801 |

| Memory_Bound : 0.05038 | Memory_Bound : 0.07006 | Memory_Bound : 0.09758 | Memory_Bound : 0.14764 | Memory_Bound : 0.23551 | Memory_Bound : 0.25875 |

| Load_Bound : 0.04975 | Load_Bound : 0.06994 | Load_Bound : 0.09756 | Load_Bound : 0.14762 | Load_Bound : 0.23547 | Load_Bound : 0.25870 |

| Load_DTLB : 0.00056 | Load_DTLB : 0.00291 | Load_DTLB : 0.00397 | Load_DTLB : 0.00647 | Load_DTLB : 0.01252 | Load_DTLB : 0.02023 |

| Load_Cache : 0.04751 | Load_Cache : 0.06600 | Load_Cache : 0.08761 | Load_Cache : 0.13781 | Load_Cache : 0.21025 | Load_Cache : 0.23244 |

| Store_Bound : 0.00063 | Store_Bound : 0.00012 | Store_Bound : 0.00002 | Store_Bound : 0.00002 | Store_Bound : 0.00004 | Store_Bound : 0.00005 |

| Store_TLB : 0.00001 | Store_TLB : 0.00001 | Store_TLB : 0.00001 | Store_TLB : 0.00002 | Store_TLB : 0.00010 | Store_TLB : 0.00004 |

| Store_Buffer : 0.00060 | Store_Buffer : 0.00011 | Store_Buffer : 0.00001 | Store_Buffer : 0.00001 | Store_Buffer : 0.00001 | Store_Buffer : 0.00001 |

| Core_Bound : 0.13732 | Core_Bound : 0.13830 | Core_Bound : 0.13109 | Core_Bound : 0.13711 | Core_Bound : 0.10326 | Core_Bound : 0.10926 |

| Interlock_Bound : 0.11610 | Interlock_Bound : 0.11333 | Interlock_Bound : 0.11263 | Interlock_Bound : 0.10552 | Interlock_Bound : 0.09648 | Interlock_Bound : 0.09286 |

| Interlock_AGU : 0.00033 | Interlock_AGU : 0.00016 | Interlock_AGU : 0.00020 | Interlock_AGU : 0.00011 | Interlock_AGU : 0.00011 | Interlock_AGU : 0.00011 |

| Interlock_FPU : 0.11562 | Interlock_FPU : 0.11310 | Interlock_FPU : 0.11235 | Interlock_FPU : 0.10536 | Interlock_FPU : 0.09633 | Interlock_FPU : 0.09271 |

| Core_Bound_Others : 0.02122 | Core_Bound_Others : 0.02498 | Core_Bound_Others : 0.01846 | Core_Bound_Others : 0.03159 | Core_Bound_Others : 0.00678 | Core_Bound_Others : 0.01639 |

| Retiring : 0.33061 | Retiring : 0.32202 | Retiring : 0.30943 | Retiring : 0.29339 | Retiring : 0.26590 | Retiring : 0.25467 |

| LD_Retiring : 0.08509 | LD_Retiring : 0.08384 | LD_Retiring : 0.07989 | LD_Retiring : 0.07608 | LD_Retiring : 0.06889 | LD_Retiring : 0.06596 |

| ST_Retiring : 0.04802 | ST_Retiring : 0.04796 | ST_Retiring : 0.04731 | ST_Retiring : 0.04436 | ST_Retiring : 0.04063 | ST_Retiring : 0.03914 |

| DP_Retiring : 0.01579 | DP_Retiring : 0.01404 | DP_Retiring : 0.01267 | DP_Retiring : 0.01211 | DP_Retiring : 0.01071 | DP_Retiring : 0.01011 |

| ASE_Retiring : 0.17804 | ASE_Retiring : 0.17281 | ASE_Retiring : 0.16650 | ASE_Retiring : 0.15789 | ASE_Retiring : 0.14306 | ASE_Retiring : 0.13700 |

| VFP_Retiring : 0.17804 | VFP_Retiring : 0.17281 | VFP_Retiring : 0.16650 | VFP_Retiring : 0.15789 | VFP_Retiring : 0.14306 | VFP_Retiring : 0.13700 |

| PC_Write_Retiring : 0.00393 | PC_Write_Retiring : 0.00350 | PC_Write_Retiring : 0.00315 | PC_Write_Retiring : 0.00302 | PC_Write_Retiring : 0.00266 | PC_Write_Retiring : 0.00251 |

| BR_IMMED_Retiring : 0.00393 | BR_IMMED_Retiring : 0.00350 | BR_IMMED_Retiring : 0.00314 | BR_IMMED_Retiring : 0.00301 | BR_IMMED_Retiring : 0.00266 | BR_IMMED_Retiring : 0.00251 |

| BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 |

| BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 |

| Metric_L1D_Miss_Ratio : 0.01534 | Metric_L1D_Miss_Ratio : 0.01732 | Metric_L1D_Miss_Ratio : 0.02081 | Metric_L1D_Miss_Ratio : 0.02163 | Metric_L1D_Miss_Ratio : 0.01878 | Metric_L1D_Miss_Ratio : 0.02113 |

| Metric_L1D_RD_Miss_Ratio : 0.01645 | Metric_L1D_RD_Miss_Ratio : 0.01864 | Metric_L1D_RD_Miss_Ratio : 0.02260 | Metric_L1D_RD_Miss_Ratio : 0.02330 | Metric_L1D_RD_Miss_Ratio : 0.02030 | Metric_L1D_RD_Miss_Ratio : 0.02284 |

| Metric_L1D_WR_Miss_Ratio : 0.00189 | Metric_L1D_WR_Miss_Ratio : 0.00186 | Metric_L1D_WR_Miss_Ratio : 0.00171 | Metric_L1D_WR_Miss_Ratio : 0.00194 | Metric_L1D_WR_Miss_Ratio : 0.00169 | Metric_L1D_WR_Miss_Ratio : 0.00189 |

| Metric_L2D_Miss_Ratio : 0.03201 | Metric_L2D_Miss_Ratio : 0.19252 | Metric_L2D_Miss_Ratio : 0.21329 | Metric_L2D_Miss_Ratio : 0.23120 | Metric_L2D_Miss_Ratio : 0.26215 | Metric_L2D_Miss_Ratio : 0.23144 |

| Metric_L2D_RD_Miss_Ratio : 0.06368 | Metric_L2D_RD_Miss_Ratio : 0.38713 | Metric_L2D_RD_Miss_Ratio : 0.42980 | Metric_L2D_RD_Miss_Ratio : 0.46448 | Metric_L2D_RD_Miss_Ratio : 0.52642 | Metric_L2D_RD_Miss_Ratio : 0.46396 |

| Metric_L2D_WR_Miss_Ratio : 0.00006 | Metric_L2D_WR_Miss_Ratio : 0.00001 | Metric_L2D_WR_Miss_Ratio : 0.00000 | Metric_L2D_WR_Miss_Ratio : 0.00000 | Metric_L2D_WR_Miss_Ratio : 0.00000 | Metric_L2D_WR_Miss_Ratio : 0.00000 |

| Metric_L3D_Miss_Ratio : 0.00041 | Metric_L3D_Miss_Ratio : 0.00010 | Metric_L3D_Miss_Ratio : 0.00089 | Metric_L3D_Miss_Ratio : 0.04055 | Metric_L3D_Miss_Ratio : 0.05405 | Metric_L3D_Miss_Ratio : 0.05183 |

| Metric_L3D_RD_Miss_Ratio : 0.00096 | Metric_L3D_RD_Miss_Ratio : 0.00021 | Metric_L3D_RD_Miss_Ratio : 0.00180 | Metric_L3D_RD_Miss_Ratio : 0.08196 | Metric_L3D_RD_Miss_Ratio : 0.10890 | Metric_L3D_RD_Miss_Ratio : 0.10425 |

| Metric_BR_Mispred_Ratio : 0.01047 | Metric_BR_Mispred_Ratio : 0.00499 | Metric_BR_Mispred_Ratio : 0.00515 | Metric_BR_Mispred_Ratio : 0.00506 | Metric_BR_Mispred_Ratio : 0.00559 | Metric_BR_Mispred_Ratio : 0.00598 |

| Metric_L1I_TLB_Miss_Ratio : 0.00001 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 |

| Metric_L1D_TLB_Miss_Ratio : 0.00084 | Metric_L1D_TLB_Miss_Ratio : 0.00414 | Metric_L1D_TLB_Miss_Ratio : 0.00577 | Metric_L1D_TLB_Miss_Ratio : 0.00980 | Metric_L1D_TLB_Miss_Ratio : 0.01345 | Metric_L1D_TLB_Miss_Ratio : 0.01641 |

| Metric_L2_TLB_Miss_Ratio : 0.00000 | Metric_L2_TLB_Miss_Ratio : 0.00001 | Metric_L2_TLB_Miss_Ratio : 0.00002 | Metric_L2_TLB_Miss_Ratio : 0.00049 | Metric_L2_TLB_Miss_Ratio : 0.02613 | Metric_L2_TLB_Miss_Ratio : 0.06261 |

| Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 |

| Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00035 | Metric_DTLB_Table_Walk_Ratio : 0.00103 |

| Metric_Load_Port_Util : 0.17019 | Metric_Load_Port_Util : 0.16767 | Metric_Load_Port_Util : 0.15977 | Metric_Load_Port_Util : 0.15216 | Metric_Load_Port_Util : 0.13779 | Metric_Load_Port_Util : 0.13191 |

| Metric_Store_Port_Util : 0.09605 | Metric_Store_Port_Util : 0.09592 | Metric_Store_Port_Util : 0.09462 | Metric_Store_Port_Util : 0.08872 | Metric_Store_Port_Util : 0.08126 | Metric_Store_Port_Util : 0.07829 |

| Metric_Neon_Port_Util : 0.35609 | Metric_Neon_Port_Util : 0.34562 | Metric_Neon_Port_Util : 0.33301 | Metric_Neon_Port_Util : 0.31577 | Metric_Neon_Port_Util : 0.28611 | Metric_Neon_Port_Util : 0.27400 |

| Metric_GFLOPs_Use : 5.69725 | Metric_GFLOPs_Use : 5.51211 | Metric_GFLOPs_Use : 5.29374 | Metric_GFLOPs_Use : 4.99903 | Metric_GFLOPs_Use : 4.53463 | Metric_GFLOPs_Use : 4.37174 |

Pack_mperf

| M=N=K=100 | M=N=K=200 | M=N=K=300 | M=N=K=500 | M=N=K=700 | M=N=K=900 |

|---|---|---|---|---|---|

| Frontend_Bound : 0.00084 | Frontend_Bound : 0.00033 | Frontend_Bound : 0.00035 | Frontend_Bound : 0.00036 | Frontend_Bound : 0.00033 | Frontend_Bound : 0.00033 |

| Fetch_Latency : 0.00084 | Fetch_Latency : 0.00033 | Fetch_Latency : 0.00035 | Fetch_Latency : 0.00036 | Fetch_Latency : 0.00033 | Fetch_Latency : 0.00033 |

| ICache_Misses : 0.00009 | ICache_Misses : 0.00006 | ICache_Misses : 0.00012 | ICache_Misses : 0.00010 | ICache_Misses : 0.00008 | ICache_Misses : 0.00008 |

| ITLB_Misses : 0.00001 | ITLB_Misses : 0.00000 | ITLB_Misses : 0.00013 | ITLB_Misses : 0.00003 | ITLB_Misses : 0.00002 | ITLB_Misses : 0.00002 |

| Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 |

| Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 |

| Bad_Speculation : 0.29067 | Bad_Speculation : 0.29156 | Bad_Speculation : 0.27964 | Bad_Speculation : 0.26751 | Bad_Speculation : 0.24406 | Bad_Speculation : 0.22907 |

| Branch_Mispredicts : 166.50000 | Branch_Mispredicts : 530.09998 | Branch_Mispredicts : 1718.09998 | Branch_Mispredicts : 7551.70020 | Branch_Mispredicts : 22910.50000 | Branch_Mispredicts : 50927.00000 |

| Backend_Bound : 0.39938 | Backend_Bound : 0.40494 | Backend_Bound : 0.43232 | Backend_Bound : 0.46649 | Backend_Bound : 0.51691 | Backend_Bound : 0.53782 |

| Memory_Bound : 0.03465 | Memory_Bound : 0.02105 | Memory_Bound : 0.05301 | Memory_Bound : 0.12115 | Memory_Bound : 0.20594 | Memory_Bound : 0.22456 |

| Load_Bound : 0.03365 | Load_Bound : 0.02057 | Load_Bound : 0.05282 | Load_Bound : 0.12086 | Load_Bound : 0.20543 | Load_Bound : 0.22408 |

| Load_DTLB : 0.00052 | Load_DTLB : 0.00052 | Load_DTLB : 0.00066 | Load_DTLB : 0.00105 | Load_DTLB : 0.00245 | Load_DTLB : 0.00548 |

| Load_Cache : 0.02941 | Load_Cache : 0.01824 | Load_Cache : 0.05483 | Load_Cache : 0.10329 | Load_Cache : 0.20224 | Load_Cache : 0.21719 |

| Store_Bound : 0.00100 | Store_Bound : 0.00048 | Store_Bound : 0.00020 | Store_Bound : 0.00029 | Store_Bound : 0.00051 | Store_Bound : 0.00048 |

| Store_TLB : 0.00004 | Store_TLB : 0.00003 | Store_TLB : 0.00003 | Store_TLB : 0.00007 | Store_TLB : 0.00010 | Store_TLB : 0.00016 |

| Store_Buffer : 0.00017 | Store_Buffer : 0.00006 | Store_Buffer : 0.00001 | Store_Buffer : 0.00001 | Store_Buffer : 0.00000 | Store_Buffer : 0.00001 |

| Core_Bound : 0.36474 | Core_Bound : 0.38389 | Core_Bound : 0.37930 | Core_Bound : 0.34534 | Core_Bound : 0.31097 | Core_Bound : 0.31327 |

| Interlock_Bound : 0.35229 | Interlock_Bound : 0.37519 | Interlock_Bound : 0.36953 | Interlock_Bound : 0.34252 | Interlock_Bound : 0.31283 | Interlock_Bound : 0.30781 |

| Interlock_AGU : 0.00153 | Interlock_AGU : 0.00081 | Interlock_AGU : 0.00102 | Interlock_AGU : 0.00058 | Interlock_AGU : 0.00056 | Interlock_AGU : 0.00057 |

| Interlock_FPU : 0.35022 | Interlock_FPU : 0.37414 | Interlock_FPU : 0.36819 | Interlock_FPU : 0.34176 | Interlock_FPU : 0.31210 | Interlock_FPU : 0.30707 |

| Core_Bound_Others : 0.01244 | Core_Bound_Others : 0.00869 | Core_Bound_Others : 0.00978 | Core_Bound_Others : 0.00282 | Core_Bound_Others : -0.00185 | Core_Bound_Others : 0.00546 |

| Retiring : 0.30911 | Retiring : 0.30317 | Retiring : 0.28769 | Retiring : 0.26564 | Retiring : 0.23871 | Retiring : 0.23278 |

| LD_Retiring : 0.04459 | LD_Retiring : 0.04036 | LD_Retiring : 0.03691 | LD_Retiring : 0.03349 | LD_Retiring : 0.02966 | LD_Retiring : 0.02869 |

| ST_Retiring : 0.00984 | ST_Retiring : 0.00510 | ST_Retiring : 0.00493 | ST_Retiring : 0.00279 | ST_Retiring : 0.00241 | ST_Retiring : 0.00230 |

| DP_Retiring : 0.02618 | DP_Retiring : 0.02283 | DP_Retiring : 0.02146 | DP_Retiring : 0.01926 | DP_Retiring : 0.01710 | DP_Retiring : 0.01657 |

| ASE_Retiring : 0.22220 | ASE_Retiring : 0.22917 | ASE_Retiring : 0.21917 | ASE_Retiring : 0.20533 | ASE_Retiring : 0.18532 | ASE_Retiring : 0.18116 |

| VFP_Retiring : 0.22220 | VFP_Retiring : 0.22917 | VFP_Retiring : 0.21917 | VFP_Retiring : 0.20533 | VFP_Retiring : 0.18532 | VFP_Retiring : 0.18116 |

| PC_Write_Retiring : 0.00675 | PC_Write_Retiring : 0.00592 | PC_Write_Retiring : 0.00538 | PC_Write_Retiring : 0.00488 | PC_Write_Retiring : 0.00430 | PC_Write_Retiring : 0.00414 |

| BR_IMMED_Retiring : 0.00674 | BR_IMMED_Retiring : 0.00592 | BR_IMMED_Retiring : 0.00537 | BR_IMMED_Retiring : 0.00487 | BR_IMMED_Retiring : 0.00429 | BR_IMMED_Retiring : 0.00414 |

| BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 |

| BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 |

| Metric_L1D_Miss_Ratio : 0.02724 | Metric_L1D_Miss_Ratio : 0.01994 | Metric_L1D_Miss_Ratio : 0.02942 | Metric_L1D_Miss_Ratio : 0.02552 | Metric_L1D_Miss_Ratio : 0.02491 | Metric_L1D_Miss_Ratio : 0.02444 |

| Metric_L1D_RD_Miss_Ratio : 0.02309 | Metric_L1D_RD_Miss_Ratio : 0.01799 | Metric_L1D_RD_Miss_Ratio : 0.02617 | Metric_L1D_RD_Miss_Ratio : 0.02342 | Metric_L1D_RD_Miss_Ratio : 0.02275 | Metric_L1D_RD_Miss_Ratio : 0.02241 |

| Metric_L1D_WR_Miss_Ratio : 0.27167 | Metric_L1D_WR_Miss_Ratio : 0.27029 | Metric_L1D_WR_Miss_Ratio : 0.28716 | Metric_L1D_WR_Miss_Ratio : 0.28674 | Metric_L1D_WR_Miss_Ratio : 0.29377 | Metric_L1D_WR_Miss_Ratio : 0.27893 |

| Metric_L2D_Miss_Ratio : 0.10546 | Metric_L2D_Miss_Ratio : 0.28792 | Metric_L2D_Miss_Ratio : 0.31292 | Metric_L2D_Miss_Ratio : 0.34867 | Metric_L2D_Miss_Ratio : 0.35318 | Metric_L2D_Miss_Ratio : 0.34909 |

| Metric_L2D_RD_Miss_Ratio : 0.22318 | Metric_L2D_RD_Miss_Ratio : 0.59666 | Metric_L2D_RD_Miss_Ratio : 0.63335 | Metric_L2D_RD_Miss_Ratio : 0.70160 | Metric_L2D_RD_Miss_Ratio : 0.70975 | Metric_L2D_RD_Miss_Ratio : 0.70086 |

| Metric_L2D_WR_Miss_Ratio : 0.00763 | Metric_L2D_WR_Miss_Ratio : 0.00597 | Metric_L2D_WR_Miss_Ratio : 0.00049 | Metric_L2D_WR_Miss_Ratio : 0.00005 | Metric_L2D_WR_Miss_Ratio : 0.00006 | Metric_L2D_WR_Miss_Ratio : 0.00021 |

| Metric_L3D_Miss_Ratio : 0.00000 | Metric_L3D_Miss_Ratio : 0.00004 | Metric_L3D_Miss_Ratio : 0.03019 | Metric_L3D_Miss_Ratio : 0.05627 | Metric_L3D_Miss_Ratio : 0.05840 | Metric_L3D_Miss_Ratio : 0.06148 |

| Metric_L3D_RD_Miss_Ratio : 0.00000 | Metric_L3D_RD_Miss_Ratio : 0.00007 | Metric_L3D_RD_Miss_Ratio : 0.06132 | Metric_L3D_RD_Miss_Ratio : 0.11355 | Metric_L3D_RD_Miss_Ratio : 0.11756 | Metric_L3D_RD_Miss_Ratio : 0.12363 |

| Metric_BR_Mispred_Ratio : 0.01086 | Metric_BR_Mispred_Ratio : 0.00510 | Metric_BR_Mispred_Ratio : 0.00516 | Metric_BR_Mispred_Ratio : 0.00507 | Metric_BR_Mispred_Ratio : 0.00574 | Metric_BR_Mispred_Ratio : 0.00609 |

| Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 |

| Metric_L1D_TLB_Miss_Ratio : 0.00222 | Metric_L1D_TLB_Miss_Ratio : 0.00231 | Metric_L1D_TLB_Miss_Ratio : 0.00293 | Metric_L1D_TLB_Miss_Ratio : 0.00301 | Metric_L1D_TLB_Miss_Ratio : 0.00385 | Metric_L1D_TLB_Miss_Ratio : 0.00481 |

| Metric_L2_TLB_Miss_Ratio : 0.00000 | Metric_L2_TLB_Miss_Ratio : 0.00049 | Metric_L2_TLB_Miss_Ratio : 0.00123 | Metric_L2_TLB_Miss_Ratio : 0.01338 | Metric_L2_TLB_Miss_Ratio : 0.07775 | Metric_L2_TLB_Miss_Ratio : 0.27862 |

| Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 |

| Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00006 | Metric_DTLB_Table_Walk_Ratio : 0.00043 | Metric_DTLB_Table_Walk_Ratio : 0.00170 |

| Metric_Load_Port_Util : 0.08919 | Metric_Load_Port_Util : 0.08072 | Metric_Load_Port_Util : 0.07381 | Metric_Load_Port_Util : 0.06698 | Metric_Load_Port_Util : 0.05932 | Metric_Load_Port_Util : 0.05737 |

| Metric_Store_Port_Util : 0.01968 | Metric_Store_Port_Util : 0.01020 | Metric_Store_Port_Util : 0.00987 | Metric_Store_Port_Util : 0.00558 | Metric_Store_Port_Util : 0.00482 | Metric_Store_Port_Util : 0.00460 |

| Metric_Neon_Port_Util : 0.44440 | Metric_Neon_Port_Util : 0.45834 | Metric_Neon_Port_Util : 0.43834 | Metric_Neon_Port_Util : 0.41067 | Metric_Neon_Port_Util : 0.37064 | Metric_Neon_Port_Util : 0.36232 |

| Metric_GFLOPs_Use : 6.73893 | Metric_GFLOPs_Use : 7.27027 | Metric_GFLOPs_Use : 6.96883 | Metric_GFLOPs_Use : 6.63430 | Metric_GFLOPs_Use : 5.88770 | Metric_GFLOPs_Use : 5.75827 |

ASM_mperf

| M=N=K=100 | M=N=K=200 | M=N=K=300 | M=N=K=500 | M=N=K=700 | M=N=K=900 |

|---|---|---|---|---|---|

| max_err:0.000000 | max_err:0.000000 | max_err:0.000000 | max_err:0.000000 | max_err:0.000000 | max_err:0.000000 |

| TAM STATIS RESULTS: | TAM STATIS RESULTS: | TAM STATIS RESULTS: | TAM STATIS RESULTS: | TAM STATIS RESULTS: | TAM STATIS RESULTS: |

| Frontend_Bound : 0.00152 | Frontend_Bound : 0.00077 | Frontend_Bound : 0.00066 | Frontend_Bound : 0.00102 | Frontend_Bound : 0.00091 | Frontend_Bound : 0.00071 |

| Fetch_Latency : 0.00152 | Fetch_Latency : 0.00077 | Fetch_Latency : 0.00066 | Fetch_Latency : 0.00102 | Fetch_Latency : 0.00091 | Fetch_Latency : 0.00071 |

| ICache_Misses : 0.00044 | ICache_Misses : 0.00016 | ICache_Misses : 0.00027 | ICache_Misses : 0.00065 | ICache_Misses : 0.00055 | ICache_Misses : 0.00037 |

| ITLB_Misses : 0.00001 | ITLB_Misses : 0.00001 | ITLB_Misses : 0.00000 | ITLB_Misses : 0.00009 | ITLB_Misses : 0.00003 | ITLB_Misses : 0.00004 |

| Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 | Predecode_Error : 0.00000 |

| Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 | Fetch_Bandwidth : 0.00000 |

| Bad_Speculation : 0.25192 | Bad_Speculation : 0.13931 | Bad_Speculation : 0.10896 | Bad_Speculation : 0.02394 | Bad_Speculation : 0.07470 | Bad_Speculation : 0.06565 |

| Branch_Mispredicts : 53.00000 | Branch_Mispredicts : 516.29999 | Branch_Mispredicts : 1237.50000 | Branch_Mispredicts : 6101.39990 | Branch_Mispredicts : 17442.59961 | Branch_Mispredicts : 37761.50000 |

| Backend_Bound : 0.09611 | Backend_Bound : 0.06685 | Backend_Bound : 0.14100 | Backend_Bound : 0.32652 | Backend_Bound : 0.41993 | Backend_Bound : 0.45994 |

| Memory_Bound : 0.06672 | Memory_Bound : 0.04390 | Memory_Bound : 0.12568 | Memory_Bound : 0.25850 | Memory_Bound : 0.40588 | Memory_Bound : 0.45154 |

| Load_Bound : 0.05526 | Load_Bound : 0.03654 | Load_Bound : 0.12134 | Load_Bound : 0.25507 | Load_Bound : 0.40223 | Load_Bound : 0.44639 |

| Load_DTLB : 0.00095 | Load_DTLB : 0.00132 | Load_DTLB : 0.00173 | Load_DTLB : 0.00268 | Load_DTLB : 0.00493 | Load_DTLB : 0.01282 |

| Load_Cache : 0.04603 | Load_Cache : 0.02975 | Load_Cache : 0.10898 | Load_Cache : 0.25344 | Load_Cache : 0.38846 | Load_Cache : 0.42574 |

| Store_Bound : 0.01146 | Store_Bound : 0.00736 | Store_Bound : 0.00434 | Store_Bound : 0.00343 | Store_Bound : 0.00365 | Store_Bound : 0.00515 |

| Store_TLB : 0.00053 | Store_TLB : 0.00058 | Store_TLB : 0.00053 | Store_TLB : 0.00086 | Store_TLB : 0.00143 | Store_TLB : 0.00289 |

| Store_Buffer : 0.00811 | Store_Buffer : 0.00488 | Store_Buffer : 0.00318 | Store_Buffer : 0.00185 | Store_Buffer : 0.00106 | Store_Buffer : 0.00071 |

| Core_Bound : 0.02938 | Core_Bound : 0.02295 | Core_Bound : 0.01532 | Core_Bound : 0.06802 | Core_Bound : 0.01405 | Core_Bound : 0.00839 |

| Interlock_Bound : 0.00353 | Interlock_Bound : 0.00220 | Interlock_Bound : 0.00274 | Interlock_Bound : 0.00144 | Interlock_Bound : 0.00120 | Interlock_Bound : 0.00117 |

| Interlock_AGU : 0.00326 | Interlock_AGU : 0.00213 | Interlock_AGU : 0.00264 | Interlock_AGU : 0.00141 | Interlock_AGU : 0.00118 | Interlock_AGU : 0.00115 |

| Interlock_FPU : 0.00000 | Interlock_FPU : 0.00000 | Interlock_FPU : 0.00000 | Interlock_FPU : 0.00000 | Interlock_FPU : 0.00000 | Interlock_FPU : 0.00000 |

| Core_Bound_Others : 0.02585 | Core_Bound_Others : 0.02075 | Core_Bound_Others : 0.01258 | Core_Bound_Others : 0.06657 | Core_Bound_Others : 0.01285 | Core_Bound_Others : 0.00722 |

| Retiring : 0.65045 | Retiring : 0.79307 | Retiring : 0.74938 | Retiring : 0.64852 | Retiring : 0.50446 | Retiring : 0.47370 |

| LD_Retiring : 0.18266 | LD_Retiring : 0.21852 | LD_Retiring : 0.20725 | LD_Retiring : 0.17772 | LD_Retiring : 0.13824 | LD_Retiring : 0.12980 |

| ST_Retiring : 0.02936 | ST_Retiring : 0.01946 | ST_Retiring : 0.01859 | ST_Retiring : 0.00998 | ST_Retiring : 0.00750 | ST_Retiring : 0.00690 |

| DP_Retiring : 0.03776 | DP_Retiring : 0.03734 | DP_Retiring : 0.03561 | DP_Retiring : 0.02792 | DP_Retiring : 0.02162 | DP_Retiring : 0.02026 |

| ASE_Retiring : 0.32465 | ASE_Retiring : 0.42233 | ASE_Retiring : 0.39544 | ASE_Retiring : 0.35224 | ASE_Retiring : 0.27398 | ASE_Retiring : 0.25727 |

| VFP_Retiring : 0.32465 | VFP_Retiring : 0.42233 | VFP_Retiring : 0.39544 | VFP_Retiring : 0.35224 | VFP_Retiring : 0.27398 | VFP_Retiring : 0.25727 |

| PC_Write_Retiring : 0.01224 | PC_Write_Retiring : 0.01246 | PC_Write_Retiring : 0.01099 | PC_Write_Retiring : 0.00911 | PC_Write_Retiring : 0.00689 | PC_Write_Retiring : 0.00636 |

| BR_IMMED_Retiring : 0.01234 | BR_IMMED_Retiring : 0.01254 | BR_IMMED_Retiring : 0.01115 | BR_IMMED_Retiring : 0.00920 | BR_IMMED_Retiring : 0.00697 | BR_IMMED_Retiring : 0.00644 |

| BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 | BR_RETURN_Retiring : 0.00000 |

| BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 | BR_INDIRECT_Retiring : 0.00000 |

| Metric_L1D_Miss_Ratio : 0.01772 | Metric_L1D_Miss_Ratio : 0.00919 | Metric_L1D_Miss_Ratio : 0.01592 | Metric_L1D_Miss_Ratio : 0.01209 | Metric_L1D_Miss_Ratio : 0.01184 | Metric_L1D_Miss_Ratio : 0.01207 |

| Metric_L1D_RD_Miss_Ratio : 0.00917 | Metric_L1D_RD_Miss_Ratio : 0.00428 | Metric_L1D_RD_Miss_Ratio : 0.01234 | Metric_L1D_RD_Miss_Ratio : 0.00928 | Metric_L1D_RD_Miss_Ratio : 0.00943 | Metric_L1D_RD_Miss_Ratio : 0.00977 |

| Metric_L1D_WR_Miss_Ratio : 0.47821 | Metric_L1D_WR_Miss_Ratio : 0.53998 | Metric_L1D_WR_Miss_Ratio : 0.27725 | Metric_L1D_WR_Miss_Ratio : 0.33759 | Metric_L1D_WR_Miss_Ratio : 0.28778 | Metric_L1D_WR_Miss_Ratio : 0.27197 |

| Metric_L2D_Miss_Ratio : 0.10307 | Metric_L2D_Miss_Ratio : 0.26791 | Metric_L2D_Miss_Ratio : 0.30925 | Metric_L2D_Miss_Ratio : 0.33934 | Metric_L2D_Miss_Ratio : 0.34121 | Metric_L2D_Miss_Ratio : 0.33642 |

| Metric_L2D_RD_Miss_Ratio : 0.21359 | Metric_L2D_RD_Miss_Ratio : 0.55121 | Metric_L2D_RD_Miss_Ratio : 0.62478 | Metric_L2D_RD_Miss_Ratio : 0.68300 | Metric_L2D_RD_Miss_Ratio : 0.68550 | Metric_L2D_RD_Miss_Ratio : 0.67536 |

| Metric_L2D_WR_Miss_Ratio : 0.00678 | Metric_L2D_WR_Miss_Ratio : 0.00421 | Metric_L2D_WR_Miss_Ratio : 0.00030 | Metric_L2D_WR_Miss_Ratio : 0.00004 | Metric_L2D_WR_Miss_Ratio : 0.00003 | Metric_L2D_WR_Miss_Ratio : 0.00006 |

| Metric_L3D_Miss_Ratio : 0.00015 | Metric_L3D_Miss_Ratio : 0.00014 | Metric_L3D_Miss_Ratio : 0.01822 | Metric_L3D_Miss_Ratio : 0.05453 | Metric_L3D_Miss_Ratio : 0.05917 | Metric_L3D_Miss_Ratio : 0.06384 |

| Metric_L3D_RD_Miss_Ratio : 0.00034 | Metric_L3D_RD_Miss_Ratio : 0.00030 | Metric_L3D_RD_Miss_Ratio : 0.03700 | Metric_L3D_RD_Miss_Ratio : 0.11009 | Metric_L3D_RD_Miss_Ratio : 0.11916 | Metric_L3D_RD_Miss_Ratio : 0.12840 |

| Metric_BR_Mispred_Ratio : 0.00552 | Metric_BR_Mispred_Ratio : 0.00864 | Metric_BR_Mispred_Ratio : 0.00648 | Metric_BR_Mispred_Ratio : 0.00745 | Metric_BR_Mispred_Ratio : 0.00798 | Metric_BR_Mispred_Ratio : 0.00826 |

| Metric_L1I_TLB_Miss_Ratio : 0.00001 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 | Metric_L1I_TLB_Miss_Ratio : 0.00000 |

| Metric_L1D_TLB_Miss_Ratio : 0.00243 | Metric_L1D_TLB_Miss_Ratio : 0.00254 | Metric_L1D_TLB_Miss_Ratio : 0.00320 | Metric_L1D_TLB_Miss_Ratio : 0.00368 | Metric_L1D_TLB_Miss_Ratio : 0.00490 | Metric_L1D_TLB_Miss_Ratio : 0.00570 |

| Metric_L2_TLB_Miss_Ratio : 0.00000 | Metric_L2_TLB_Miss_Ratio : 0.00002 | Metric_L2_TLB_Miss_Ratio : 0.00007 | Metric_L2_TLB_Miss_Ratio : 0.01111 | Metric_L2_TLB_Miss_Ratio : 0.04116 | Metric_L2_TLB_Miss_Ratio : 0.20023 |

| Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 | Metric_ITLB_Table_Walk_Ratio : 0.00000 |

| Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00000 | Metric_DTLB_Table_Walk_Ratio : 0.00003 | Metric_DTLB_Table_Walk_Ratio : 0.00035 | Metric_DTLB_Table_Walk_Ratio : 0.00190 |

| Metric_Load_Port_Util : 0.36531 | Metric_Load_Port_Util : 0.43704 | Metric_Load_Port_Util : 0.41450 | Metric_Load_Port_Util : 0.35545 | Metric_Load_Port_Util : 0.27647 | Metric_Load_Port_Util : 0.25961 |

| Metric_Store_Port_Util : 0.05872 | Metric_Store_Port_Util : 0.03892 | Metric_Store_Port_Util : 0.03719 | Metric_Store_Port_Util : 0.01995 | Metric_Store_Port_Util : 0.01500 | Metric_Store_Port_Util : 0.01381 |

| Metric_Neon_Port_Util : 0.64930 | Metric_Neon_Port_Util : 0.84466 | Metric_Neon_Port_Util : 0.79088 | Metric_Neon_Port_Util : 0.70447 | Metric_Neon_Port_Util : 0.54795 | Metric_Neon_Port_Util : 0.51453 |

| Metric_GFLOPs_Use : 10.20137 | Metric_GFLOPs_Use : 13.45224 | Metric_GFLOPs_Use : 12.57732 | Metric_GFLOPs_Use : 10.50762 | Metric_GFLOPs_Use : 8.73145 | Metric_GFLOPs_Use : 8.13339 |

术语表

TMA: 也即 Top-down Microarchitecture Analysis 的缩写。TMA 是 intel 工程师为分析 intel X86 cpu 微架构的性能瓶颈而总结的方法论,可参见 intel x86 TMA 。一句话总结的话,TMA 就是一种在微架构层面自顶而下的瓶颈定位方法。mperf 在 ARM cpu 上实现了 TMA 的方法论,并进行了包括本文在内的实践验证。

Core_Bound: This metric represents fraction of slots where Core non-memory issues were of a bottleneck. Shortage in hardware compute resources; or dependencies in software"s instructions are both categorized under Core Bound. 表示 CPU 处理器后端非访存相关的 stall 引起的性能损失,通常包括 ALU 单元的资源不足,以及流水线上的指令依赖引起的 stall 等。

Interlock_Bound: No operation issued due to the backend interlock. 表示 CPU 处理器后端因为发生了pipeline interlock而产生的 stall, pipeline interlock 就是 A 指令的执行依赖 B 指令某一个 pipeline stage 的结果,而 B 指令还没有执行到对应 stage,指令 A 就等 stall 等待依赖条件满足,比如 raw 依赖。考虑到本文中频繁出现关于处理器 pipeline 以及 pipeline interlock 相关的术语,如果读者对这部分概念比较模糊,推荐一个很好的教学文档 mips pipeline 。

Interlock_FPU: No operation issued due to the backend, interlock, FPU. This event counts every cycle that issue is stalled and there is an interlock that is due to an FPU/NEON instruction. 这个指标是上面 Interlock_Bound 的子类别,表征由 FPU/NEON 指令的 pipeline interlock 而产生流水线停顿的比例,比如前文降低 Interlock_FPU 的试验中,如果循环体中只有一个

fmla v0.4s, v0.4s, v0.4s指令,下一个循环 iter 的 fmla指令需要读取 v0 的数值,这就依赖上一个 iter 的 fmla 指令更新完 v0,而 fmla 指令的 latency 是多个 cycle,也就造成了相邻 iter 见 fmla 指令的 interlock, 流水线中将产生大量 stall。Load_Cache: No operation issued due to the backend, load, Cache miss. 表征因为Cache读延迟导致的stall。

Metric_Neon_Port_Util: 处理器后端 neon port 的利用率,计算公式是ASE_SPEC/(CYCLES*NEON_PORTS),拿实际执行的neon指令数除以处理器运行的cycle和处理器后端支持neon操作的port端口数的乘积,ARM a55的NEON_PORTS是1,在这里用于表征处理器neon单元的利用率。

Metric_L3D_RD_Miss_Ratio: L3 Cache读的缺失率,计算公式是L3D_CACHE_REFILL_RD/L3D_CACHE_RD。

Metric_Load_Port_Util: 处理器后端 load port 的利用率,计算公式是LD_SPEC/(CYCLES*LD_PORTS),拿实际执行的load指令数除以处理器运行的cycle数和处理器后端支持load操作的port端口数的乘积,ARM a55的LD_PORTS是1,在这里用于表征处理器LD单元的利用率。

L1D_TLB_Miss_Ratio: 表征的是L1D的TLB miss的比例,L1D TLB miss会触发L2D TLB的read。

L2D_TLB_REFILL: 表征的是L2D的TLB miss的数量,会触发昂贵的 page table walker。

关键词:

-

-

-

-

记录--vue刷新当前页面

全球关注:借助 mperf 进行矩阵乘法极致优化

MySQL学习笔记-存储引擎

当前看点!低代码起势,开发者可以早日脱离996了?

今日热议:南钢股份:钢材销量同比下降6.28%,2022年年归母净利润同比下滑48.59%,拟10派2.5元

快讯:《生化危机4:重制版》D加密惹争议 又导致性能问题了

全球观热点:女子地铁照被AI一键脱衣传播 网友:无下限的开发

每日焦点!网友准备冲Redmi Note 12 Turbo哈利·波特版:预算3900元

头条:男子乘错出租车 起步1秒被强制收费6元:走了不到10米

【世界新视野】内存掉入无底洞:没有最便宜 只有更便宜

环球观天下!32、K8S-配置管理之Configmap

世界看点:Python中21道个程序小练习

css设置超过固定长度以省略号显示

全球看点:乒乓球技巧训练这就是高手的水准_乒乓球技巧

全球简讯:瑞银:看好亚股增长潜力 偏好亚洲投资级债券

Twitter将上线离谱新规:非会员甚至无法参与投票

热头条丨九识自动驾驶物流车被曝闯红灯 网友:该怎么记分处罚

速读:“网红”威震天在北京环球影城摔了一跤 客服回应:后续演出正常

【环球新要闻】一个时代结束了!Wii U和3DS在线商店已正式关闭

实时:透明外壳设计!Nothing Ear(2)无线耳机上市 999元

热资讯![HTML]表单标签(form表单域、input输入表单、label标签、select下拉表单、textarea文本域)

C#List的3种排序方法

环球观焦点:韩国有意解禁福岛水产品?在野党呼吁韩总统表态

全球新资讯:收评:两市震荡走弱沪指跌0.19% 人工智能概念冲高回落

全球热头条丨想玩必须升级!Steam将于2024年终止对Win7/8/8.1系统支持

中国科学家发现月球水库 估计蓄水量多达2700亿吨

父母做生意给儿子取名为顾客 当事人:家里有个“顾客”能带来更多顾客

世界最高安全标准 我国自研核电华龙一号西部首堆全面建成

【时快讯】249元 TP-LINK推出新款玄鸟AX3000路由器:3000Mbps满血Wi-Fi 6

观热点:Rust 备忘清单_开发速查表分享

即时焦点:郑州大学河南先进技术研究院2023年硕士研究生拟调剂信息公告已公布

天天热点评!国服一步步被掏空 暴雪国际服支持微信支付宝:价格全面上涨

vivo X Fold2将在博鳌亚洲论坛首秀:采用“天圆地方·两仪万象”设计

每日资讯:网信办:全面清理虚假摆拍短视频

环球观热点:如何应对上手英文工具站的 8 大误区

小程序的车载场景应用

【Visual Leak Detector】配置项 ReportEncoding

数据建模

世界要闻:在.NET7使用NPOI读取Excel如此简单

每日简讯:西门子医疗Syngo Carbon助力贵安医院打破数据孤岛,加速智慧医院建设

每日快播:谁是更好的甜点处理器?锐龙5 7600、酷睿i5-13400对比评测:游戏差距大到不敢相信

终于结束了 特斯拉“退一赔三”案二审败诉后申请再审:法院驳回

笔记本电脑排风扇声音大是怎么回事?笔记本电脑排风扇声音大怎么解决?

nova6最严重的缺点是什么?nova6参数详细价格

哈尔滨有几个电脑城?哈尔滨电脑城地址

折旧率是什么意思?折旧率计算公式

全球今头条!Go语言:通过TDD驱动测试开发为同事写的程序优化提速——初次接触并发与channel

【世界时快讯】非看不可的Redis持久化

选择排序

速递!【Visual Leak Detector】配置项 MaxTraceFrames

flash8怎么下载到电脑上?Flash8的序列号是多少?

大连地铁敞门行驶 线路刚开12天:客服称“原因正在调查”

快资讯丨00后女生毕业当猪场保育员:她认为这行业很有潜力

世界快资讯丨微软反戈一击 反垄断战火引至日本本土

当前头条:东南亚出游降温:机票降幅达40%

环球新动态:机器学习基础06DAY

数据密集型应用存储与检索设计

当前头条:范畴论:迷人的数学花园

环球观天下!智能存储重磅上线:低成本闲时转码

【天天快播报】促消费,振内需,康佳加速业务高质量发展

世界第一名宇航员!尤里·加加林坠机遇难地点照片首次公开

每日看点!真的可以免费坐高铁了!用12306积分兑换:官方教程收好

焦点速递!杭州地铁现打工人专线 网友:通勤都不让闲着

环球观察:《指环王:力量之戒》片场马匹死亡 动保组织谴责:剥削动物

魅族20系列大杯曝光:120Hz E6直屏、12GB+512GB组合

焦点快报!实验一 密码引擎-2-电子钥匙功能测试

CNStack 虚拟化服务:实现虚拟机和容器资源的共池管理

每日视讯:ChatGPT软件技术栈解密

天天微速讯:具有FTP、FTPS和sftp功能的文本编辑器——EditPlus功能介绍

今日热搜:【解答】MySQL MTR的实现原理与优势

核磁共振增强剂的危害_核磁共振增强剂的危害

环球热文:高德、阿里云发布全新车路协同方案 夜间开车像开了上帝视角

世界热文:瑞幸咖啡被吐槽喝完3口剩下全是冰 客服:门店按配方比例制作

世界快消息!育碧正式宣布“单飞”:E3展会再失重要参展商

独此一家!真我GT Neo5 SE梦幻续航组合:100W快充+5500mAh电池

每日速递:迪士尼《小美人鱼》真人电影确认引进内地:或5月上映

世界短讯!关于ChatGPT的一些信息,我画了一张思维导图

当前头条:前端设计模式——解释器模式

世界热点!各部队加强即将退役人员保密教育的一组见闻

焦点速递!男子2天喝4顿后死亡 起诉店家获赔:医生称如此喝酒很伤身

全球实时:价格相差数倍!智能手表比智能手环强在哪里?

昔日明星掌机落幕:任天堂正式关闭3DS游戏商店

最新消息:李想:攻破燃油车 需3步

当前简讯:任天堂爆款续作!《塞尔达传说:王国之泪》新实机今晚公布:5月12日发售

全球今热点:头铁面试官:一个小小的 System.out.println 硬是考了我半个小时,被问懵了。。

【天天播资讯】《Flask Web 开发指南 pt.1》

环球信息:日本北海道一养鸡场发生禽流感疫情

库克喊话:苹果和中国市场30年来密切关联 我们相互成长

今日热讯:告别物理卡槽!iPhone 15将进一步普及eSIM:水货机今后更难了

老人推倒摩托继承人被判赔1.6万元:车主直言被网曝 老人违法不该被宽恕

全球简讯:【国际大宗商品早报】隔夜外盘商品大面积反弹 美油涨超5%芝加哥农产品全线上涨

全球快报:最“丑”绿色车牌或在2年内取消 网友热议电车优待早该结束!国人将车牌代表面子

全球信息:2022年中国市场最畅销10款手机:国人狂买iPhone 13 高端安卓泪奔

天天视讯!昔日超市霸主 家乐福中国内地首店关闭:在北京开了28年

焦点快播:禁售时间已明确 油车还能开多久?中石油回应:新能源拐点还有很长路

天天微头条丨读Java性能权威指南(第2版)笔记30_Java服务器

世界热点评!Linux -mv命令的10个实用例子

全球看热讯:日本动漫演唱会_日本动漫

环球信息:【Visual Leak Detector】配置项 MaxDataDump

C++ 整理