最新要闻

- 环球头条:899元 雷蛇帝王蝶鼠标垫发布:钢化玻璃一体成型

- 天天微速讯:6岁女童看店 2人用98元买走60根虫草引热议:无耻不道德行为、交易无效

- 全球简讯:特斯拉不好惹!网红车评人“蔡老板”被判道歉赔10万后:维持原判 不得上诉

- 落地成盒!苹果可折叠手机新专利:掉落自动闭合

- 环球观察:又一网红店翻车 半天妖烤鱼被曝垃圾桶捞回餐食又端上桌 你吃过没

- 全球短讯!iQOO Z7对标旗舰配置:OIS光学防抖、NFC全都有

- 性价比领先RTX 3060多达78% Intel Arc新驱动优化《暗黑4》等游戏

- 造谣蔚来因质量失控酿车祸 车评人被判向蔚来道歉、赔偿8万元

- 全球快报:发放37亿元购车补贴 单车最高降价5万!上汽大众回应

- 焦点速读:58元 国产单机游戏《二分之一》正式发售:近百位角色 文本超25万字

- 【时快讯】好多人说驱鼠器不管用是真的吗为什么(好多人说驱鼠器不管用是真的吗)

- 女子地铁上辱骂殴打男子 通报来了:拘留10天 罚款500

- 动物园母猴产后啃食夭折小猴 工作人员:有一定野性、比较常见

- 环球讯息:零百加速1.9秒 中国第一超跑埃安Hyper SSR量产已达50%

- 消息!别喝工业水啤了:熊猫精酿杀马特扯皮小麦啤酒6听19.9元大促

- 全球微速讯:20.98万起大杀四方 新款比亚迪唐DM-i、汉EV上市当日狂卖8196台

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

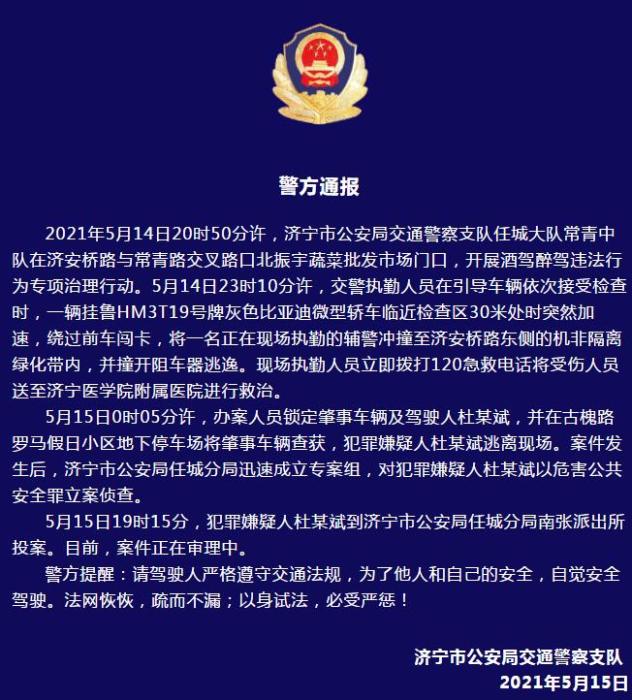

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

热议:zynq基于DMA的串口传图

(资料图片)

(资料图片)

小梅哥的这个ZYNQ开发板上的DDR3位于PS侧,PL侧想要使用DDR3作为缓存的话,得通过HP接口来与PS侧的DDR3控制进行通信。本次实验在小梅哥OV5640工程的基础上,通过修改VDMA的S2MM端的模块而来的。将VMDA的帧缓存区设为1,关闭帧同步的功能后,其实和DMA差不多。

一、需要自定义的ip核

这里列出的为自己写的IP核。小梅哥的工程里还用到了其它的自定义的IP核,这里就不列出了。

1、串口接收图像数据模块

该模块调用了之前写的串口8位接收模块,详情可点击查看。此外,本模块还调用16位宽、深度为1024的带数据计数的普通FIFO核该模块主要的思想就是将接收到的两个8位的数据拼接位1个16位的数据并存入FIFO中,当存入的数据达到LINE_LENGTH(800)的时候,在收到从接口的准备信号时一次性写入VMDA中,再通过VMDA将数据写到DDR3中。此外该模块在应用的时候要封装成带AXI4_Stream 接口的IP核,具体封装过程可网上找教程。

`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company: GDUT// Engineer: Lclone// // Create Date: 2023/02/07 20:38:34// Design Name: // Module Name: Img_Rx// Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision:// Revision 0.01 - File Created// Additional Comments:// //////////////////////////////////////////////////////////////////////////////////module Img_Rx# (parameter RX_BAUD = 115200, parameter CLK_FQC = 50_000_000, parameter LINE_LENGTH = 800) ( input Uart_Rx, //--------------------------- input m_clk, input m_axis_aresetn, output [15:0] m_axis_tdata, output reg m_axis_tlast, input m_axis_tready, output reg m_axis_tvalid ); wire [7:0] Uart_Data; wire Rx_done; reg Rx_done_r; reg Rx_done_cnt; reg [15:0] Uart_Data_16; wire [9:0] fifo_data_count; reg [9:0] out_data_count; reg m_axis_tvalid_r; reg [18:0] cnt_1ms; always @(posedge m_clk) Rx_done_r <= Rx_done; always @(posedge m_clk) m_axis_tvalid <= m_axis_tvalid_r; always @(posedge m_clk or negedge m_axis_aresetn) begin if(m_axis_aresetn == 0) Uart_Data_16 <= 0; else if(Rx_done == 1) Uart_Data_16 <= {Uart_Data_16[7:0],Uart_Data}; end always @(posedge m_clk or negedge m_axis_aresetn) begin if(m_axis_aresetn == 0) Rx_done_cnt <= 0; else if(Rx_done == 1) Rx_done_cnt <= Rx_done_cnt + 1"b1; else Rx_done_cnt <= Rx_done_cnt; end always @(posedge m_clk or negedge m_axis_aresetn) begin if(m_axis_aresetn == 0) m_axis_tvalid_r <= 0; else if(m_axis_tready == 1 & fifo_data_count >= LINE_LENGTH) m_axis_tvalid_r <= 1"b1; else if(fifo_data_count <= 1) m_axis_tvalid_r <= 0; else m_axis_tvalid_r <= m_axis_tvalid_r; end always @(posedge m_clk or negedge m_axis_aresetn) begin if(m_axis_aresetn == 0) out_data_count <= 0; else if(out_data_count == LINE_LENGTH - 1) out_data_count <= 0; else if(m_axis_tvalid_r & m_axis_tready) out_data_count <= out_data_count + 1"b1; else out_data_count <= out_data_count; end always @(posedge m_clk or negedge m_axis_aresetn) begin if(m_axis_aresetn == 0) m_axis_tlast <= 0; else if(out_data_count == LINE_LENGTH - 1) m_axis_tlast <= 1; else m_axis_tlast <= 0; end always @(posedge m_clk or negedge m_axis_aresetn) begin if(m_axis_aresetn == 0) cnt_1ms <= 0; else if(cnt_1ms == 500000 - 1) cnt_1ms <= 0; else cnt_1ms <= cnt_1ms + 1"b1; end uart_byte_rx # ( .RX_BAUD (RX_BAUD), .CLK_FQC (CLK_FQC)) uart_byte_rx_inst ( .Clk (m_clk), .Rst_n (m_axis_aresetn), .Uart_rx (Uart_Rx), .Data (Uart_Data), .Rx_done (Rx_done) ); fifo_generator_0 fifo_generator_0_inst ( .clk(m_clk), // input wire clk .srst(~m_axis_aresetn), // input wire srst .din(Uart_Data_16), // input wire [15 : 0] din .wr_en(~Rx_done_cnt & Rx_done_r), // input wire wr_en .rd_en(m_axis_tvalid_r & m_axis_tready), // input wire rd_en .dout(m_axis_tdata), // output wire [15 : 0] dout .full(), // output wire full .empty(), // output wire empty .data_count(fifo_data_count) // output wire [9 : 0] data_count);endmodule2、模块仿真

(1)仿真激励

`timescale 1ns / 1psmodule rx_img_test(); reg clk_50m;initial clk_50m <= 1;always #10 clk_50m <= ~clk_50m;reg rst_n;initial begin rst_n <= 0; #200 rst_n <= 1;end wire [15:0] m_axis_tdata;wire m_axis_tlast;wire m_axis_tready;wire m_axis_tvalid;wire [15:0] out_axis_tdata;wire out_axis_tlast;wire out_axis_tready;wire out_axis_tvalid;reg Uart_Rx;reg [ 7:0] Uart_Data;Img_Rx #( .RX_BAUD(2_000_000), .CLK_FQC(100_000_000), .LINE_LENGTH(16)) Img_Rx_inst ( .Uart_Rx(Uart_Rx), // input wire Uart_Rx .m_clk(clk_50m), // input wire m_clk .m_axis_aresetn(rst_n), // input wire m_axis_aresetn .m_axis_tdata(m_axis_tdata), // output wire [15 : 0] m_axis_tdata .m_axis_tlast(m_axis_tlast), // output wire m_axis_tlast .m_axis_tready(m_axis_tready), // input wire m_axis_tready .m_axis_tvalid(m_axis_tvalid) // output wire m_axis_tvalid); axis_data_fifo_0 axis_data_fifo_0_inst ( .s_axis_aresetn(rst_n), // input wire s_axis_aresetn .s_axis_aclk(clk_50m), // input wire s_axis_aclk .s_axis_tvalid(m_axis_tvalid), // input wire s_axis_tvalid .s_axis_tready(m_axis_tready), // output wire s_axis_tready .s_axis_tdata(m_axis_tdata), // input wire [15 : 0] s_axis_tdata .s_axis_tlast(m_axis_tlast), // input wire s_axis_tlast .m_axis_tvalid(out_axis_tvalid), // output wire m_axis_tvalid .m_axis_tready(out_axis_tready), // input wire m_axis_tready .m_axis_tdata(out_axis_tdata), // output wire [15 : 0] m_axis_tdata .m_axis_tlast(out_axis_tlast) // output wire m_axis_tlast);initial begin Uart_Rx <= 1; Uart_Data <= 0; #200 repeat (256) begin data_deliver(Uart_Data); Uart_Data = Uart_Data + 1; end $stop;endtask data_deliver; input [7:0]test_data; begin Uart_Rx <= 1"b0; #1000 Uart_Rx <= test_data[0]; #1000 Uart_Rx <= test_data[1]; #1000 Uart_Rx <= test_data[2]; #1000 Uart_Rx <= test_data[3]; #1000 Uart_Rx <= test_data[4]; #1000 Uart_Rx <= test_data[5]; #1000 Uart_Rx <= test_data[6]; #1000 Uart_Rx <= test_data[7]; #1000 Uart_Rx <= 1"b1; #1000; endendtaskassign out_axis_tready = 1;endmodule(2)仿真结果

可见该模块能够正确地将16个两字节的数据正确的输出,并在最后一个数据的位置基于一个tlast信号。

二、工程修改

打开小梅哥的ACZ7020的OV5640_LCD工程,然后将红框部分的模块删除,加入自定义的串口接收图像数据模块。并修改下列IP核的参数将频率修改为如下:将帧缓存区设为1Fsync Options选择None,关掉帧同步功能在约束文件中,加入串口的管脚约束在SDK中,将OV5640的初始化函数删除,将PS_IIC和OV5640库删除同时也将PS_IIC和OV5640库的路径删除掉然后就可以下载程序到开发板上了

三、上板验证

将程序下载进开发板,然后打开img2lcd软件,读取一个800*480大小的BMP文件,并按如下设置:然后在输出的文件中进行修改删除首行删除末尾符号使用软件的查找替换功能,将所有的0X删掉,并将","换为空格符,然后使用行操作里面的行合并去除掉每一行末尾的回车符。最后就得到传输的图像数据:打开友善串口调试助手,将图像数据复制进去,打开串口端口,设置好波特率,然后发送,确保TX发送了768000个字节,否则图像会错位;确保底下绿色的字显示的波特率为115200,否则数据无法正确传输。传输数据后,发现图像能够正确显示在LCD上实验成功。本随笔还有许多小细节没有给出,如果遇到问题,可以评论询问。

关键词:

-

-

-

-

热议:zynq基于DMA的串口传图

天龙八部单机版怎么下载?天龙八部单机版武功搭配

环球头条:899元 雷蛇帝王蝶鼠标垫发布:钢化玻璃一体成型

天天微速讯:6岁女童看店 2人用98元买走60根虫草引热议:无耻不道德行为、交易无效

全球简讯:特斯拉不好惹!网红车评人“蔡老板”被判道歉赔10万后:维持原判 不得上诉

落地成盒!苹果可折叠手机新专利:掉落自动闭合

环球观察:又一网红店翻车 半天妖烤鱼被曝垃圾桶捞回餐食又端上桌 你吃过没

今头条!python 排序算法

天天通讯!uni-app 实现轮播图组件父容器背景色随图片主题色改变

全球短讯!iQOO Z7对标旗舰配置:OIS光学防抖、NFC全都有

性价比领先RTX 3060多达78% Intel Arc新驱动优化《暗黑4》等游戏

造谣蔚来因质量失控酿车祸 车评人被判向蔚来道歉、赔偿8万元

全球快报:发放37亿元购车补贴 单车最高降价5万!上汽大众回应

焦点速读:58元 国产单机游戏《二分之一》正式发售:近百位角色 文本超25万字

【时快讯】好多人说驱鼠器不管用是真的吗为什么(好多人说驱鼠器不管用是真的吗)

热点在线丨前端操作cookie的用法

世界最新:数据湖选型指南|Hudi vs Iceberg 数据更新能力深度对比

快讯:全网最详细中英文ChatGPT接口文档(四)30分钟快速入门ChatGPT——Models模型

git回退到某个提交

世界微头条丨交易商协会对中航租赁予以通报批评

女子地铁上辱骂殴打男子 通报来了:拘留10天 罚款500

动物园母猴产后啃食夭折小猴 工作人员:有一定野性、比较常见

环球讯息:零百加速1.9秒 中国第一超跑埃安Hyper SSR量产已达50%

消息!别喝工业水啤了:熊猫精酿杀马特扯皮小麦啤酒6听19.9元大促

全球微速讯:20.98万起大杀四方 新款比亚迪唐DM-i、汉EV上市当日狂卖8196台

【全球聚看点】Java 枚举实现单例模式,线程安全又优雅!

天天讯息:前端设计模式——组合模式

全球快播:[issues] webrtc 接入SRS丢包率不正确问题

天天热资讯!你居然还不会判定表法?

资讯:【微电平台】-高并发实战经验-奇葩问题解决之旅

快递员骑摩托与特斯拉相撞当场身亡 现场惨烈:司机喊话车没失控

焦点短讯!大众最便宜电车来了!截胡特斯拉Model Q

天天要闻:生财有道?特斯拉圆形方向盘开卖:售价4800元

德系不装了!上汽大众全系车型开降:最多补贴5万元

当前热讯:超5000米 世界最高海拔风电场发电量超1亿度 中国再创纪录

【天天聚看点】济南遥墙国际机场二期改扩建工程项目房屋征收范围确定

每日时讯!Linux进程通信 | 消息队列

天天时讯:银行援助方案缓解市场担忧 美债收益率普遍回升

天天最资讯丨苏南硕放机场更名无锡苏州机场?官方回应:没改名

世界观焦点:大学生组团到工地吃13元盒饭 20种菜任选味道棒:老板回应物美价廉不怕竞争

迄今最好的长焦旗舰!OPPO Find X6系列来了

摊上事:联想被判向美国公司赔偿近10亿授权费 侵犯5G专利等

【天天新要闻】我国率先研发 全球6G技术大会即将召开:2030年商用

读Java性能权威指南(第2版)笔记19_垃圾回收F

【全球独家】聊聊缓存

环球动态:自动驾驶驶向何方

天天动态:高通胀正掏空美国人储蓄 近半民众陷入财务困境:鸡蛋都吃不起节奏

为了改桥接,我决定破解中兴F450G V2光猫

每日快报!贵州贵阳多地突降冰雹!现场视频画面:还伴随闪电

国内成品油零售价今晚即将下调:预计下跌0.05元/升!

世界新动态:体验完百度的文心一言 我只能说:它胆子够大!

天天热点评!好评率98%的民国武侠动作游戏:终于要上手游了!

天天观焦点:生产力起飞!微软正式推出Microsoft 365 Copilot:AI全面植入Office全家桶

据报道 特斯拉Model S的纽伯格林赛道比保时捷Taycan还快

NodeJS 实战系列:模块设计与文件分类

环球新动态:计算,存储,网络虚拟化区别

当前热门:加速颠覆燃油车!汉、唐冠军版上市:双车20.98万起

全球快看:从小吃到大的腌菜 竟是“垃圾堆”生产?被315暴击的进来

即时看!MyBatis

当前快看:群友们的表情包《九十期》

每日视点!男子镜头前嗨舞被羊顶翻 网友看完大笑:做人不能太狂浪

每日头条!自媒体捏造董明珠和王自如恋情!龚文祥公开致歉:希望取得原谅

今日快看!Win11最新正式版闯大祸:SSD性能不忍直视

新动态:设计一款可扩展和基于windows系统的一键处理表格小工具思路

天天即时看!微软签署第四份《使命召唤》十年协议:索尼仍不愿妥协

【天天聚看点】男孩长蛀牙爸爸用电钻钻牙止痛 被网友疯狂指责:太危险了

全球讯息:20.98万元起 2023款比亚迪唐DM-i上市:全系升级铝合金悬架

热点聚焦:冲击百万销量!比亚迪汉DM-i、DM-p补贴10000元现金

世界观速讯丨点积、内积、外积、叉积、张量积——概念区分

day05-Lombok、SpringInitializer

【世界聚看点】国家推出稳定2023年大豆生产一揽子支持政策

当前关注:双拖布+超大吸力!小米米家扫拖机器人3S发售:千元旗舰

世界视点!特斯拉一体化压铸工艺被质疑增加修车成本 一个小碰撞可能要修11万

精彩看点:追上Intel AMD锐龙7000处理器终于用上192GB内存:频率满血

环球看热讯:315全景观察:深情主播“连哄带骗” 爸妈的钱就没了

最新:无解了!微软将推出基于GPT-4的Office 365服务 实用性拉满

【焦点热闻】北京通州区汽车消费券活动时间是什么时候?

Redis监控

sed文本处理工具常见用法

每日看点!Prometheus 监控系统1

Java中的NIO

环球快报:带你全方面了解字节 A/B 实验的文化与工具

世界新资讯:【金融街发布】交易商协会发布企业资产证券化基础性制度

【世界播资讯】重庆龙凤胎熊猫宝宝取名“渝可”“渝爱”

速看:《小美人鱼》剧照还原动画经典场景:就是肤色不太对

头条焦点:中国制造!索尼第四代降噪豆XM5佩戴/音质/快充全面升级:AirPods Pro2劲敌

老人墓中藏13万现金全部霉变 专业能手全力抢救:官方科普纸钞如何保管

海底捞部分门店取消免费美甲:只能付费购买穿戴甲

视讯!SQLMap 源码阅读

今日观点!abc285G

环球精选!JVM -Xss

【高端访谈·城市力量】“双碳”背景下农商银行如何“点绿”成金?——访秦农银行党委书记、董事长李彬

今热点:五菱电动“吉姆尼” 宝骏悦也续航里程公布:能跑303公里

董明珠要玩大的?格力成立房地产新公司 投资数亿元

东方甄选称被骗了 虾品供应商发声:不认可甩锅行为

热点在线丨百度文心一言申请页被挤爆:预约1小时涌入3万企业

环球快讯:现实版GTA!美劫匪偷直升机因操作失误当场坠毁:一地碎片

国宝大熊猫的视频_国宝大熊猫的故事

66.类型转换

快讯:【0基础学爬虫】爬虫基础之抓包工具的使用