最新要闻

- 世界播报:满江红票房破21亿!张艺谋揭秘震撼结尾 片方发声明称偷票房等指责纯属造谣

- 天天简讯:辽宁上空惊现“三个太阳”幻日奇观 手机拍下罕见一幕:专家揭秘成因

- 当前滚动:小朋友哈尔滨室外舔冰雕舌头被粘:东北的冰真的是甜的吗?

- 环球热议:信号大升级!iPhone 15系列有望支持Wi-Fi 6E传输标准

- 世界最资讯丨核显的春天来了!SK海力士发布最快LPDDR5T内存:飙上9.6Gbps

- 每日看点!明年再见!充电器一拔我和浪浪山道别了引热议 专家建议春节假期延至9天

- 东南亚赚大:中国游客彻底抛弃日本、韩国 这波打击影响太惨

- 全球速看:一家5人花100块去看“时空隧道” 直言开心就值:网友调侃参观蔬菜大棚

- 京东最便宜2TB SSD秒杀:569元还是TLC颗粒

- 世界新消息丨票房超19亿!网友质疑《满江红》剧情抄袭《龙门镖局》 10年前梗都照搬

- 全球头条:日本公司推出懒人沙发:走哪躺哪

- 环球滚动:还要更便宜!特斯拉:近5年车辆平均售价已减半 将继续控制成本

- 环球热消息:新增万名雇员!2022年荷兰半导体巨头ASML营收破纪录

- 【快播报】驾驶辅助技能大比拼 特斯拉殿后

- 获11年来最大营收增幅照裁不误:IBM宣布将裁员3900人

- 世界快讯:苹果官网开售Mac Studio“锁具套装”:一个密码锁卖到548元

广告

手机

iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

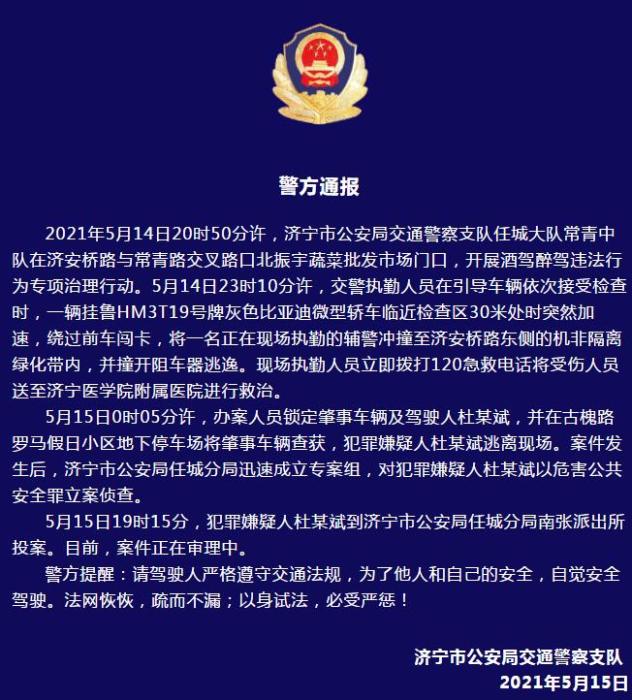

警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- iphone11大小尺寸是多少?苹果iPhone11和iPhone13的区别是什么?

- 警方通报辅警执法直播中被撞飞:犯罪嫌疑人已投案

- 男子被关545天申国赔:获赔18万多 驳回精神抚慰金

- 3天内26名本土感染者,辽宁确诊人数已超安徽

- 广西柳州一男子因纠纷杀害三人后自首

- 洱海坠机4名机组人员被批准为烈士 数千干部群众悼念

家电

每日简讯:用状态机实现通用多字节SPI接口模块

(资料图片)

(资料图片)

这次设计一个通用的多字节SPI接口模块,特点如下:

- 可以设置为1-128字节的SPI通信模块

- 可以修改CPOL、CPHA来进行不同的通信模式

- 可以设置输出的时钟状态转移图和思路与多字节串口发送模块一样,这里就不给出了,具体可看该随笔。

一、模块代码

1、需要的模块

通用8位SPI接口模块

`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company: // Engineer: Lclone// // Create Date: 2023/01/23 00:56:52// Design Name: SPI_Interface// Module Name: SPI_Interface// Project Name: // Target Devices: // Tool Versions: // Description: // SPI接口模块// 可修改分频参数来生成目标频率,最低分频系数为2;// 可以置位CPOL、CPHA可以来设置通信模式;// 本模块只有1位,但是可以简单修改位宽来设置多位片选信号// Dependencies: // // Revision:// Revision 0.01 - File Created// Additional Comments:// //////////////////////////////////////////////////////////////////////////////////module SPI_Interface# ( parameter Value_divide = 2)//分频系数(最低为2) ( //-----------------内部接口------------------ input Clk, //时钟 input Rst_n, //复位信号 input CPOL, //时钟极性 input CPHA, //时钟相位 input CS_input, //片选信号 input Send_en, //发送使能 input [7:0] Data_send, //待发送数据 output reg Read_en, //接收数据读使能 output reg [7:0] Data_recive, //接收到的数据 //------------------外部接口------------------ output reg Spi_clk, //输出时钟端 output reg Spi_mosi, //主输出从接收端 input Spi_miso, //主接收从输出端 output Cs_output //片选信号输出 ); reg act_flag; //活动状态寄存器 reg [9:0] cnt_divide; //分频计数器 reg [7:0] Data_send_reg; //带发送数据寄存器 reg [4:0] cnt_pulse; //脉冲计数器 always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) act_flag <= 0; else if(Send_en == 1) act_flag <= 1; else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1 & cnt_pulse == 16) act_flag <= 0; else act_flag <= act_flag; end always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) Read_en <= 0; else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1 & cnt_pulse == 16) Read_en <= 1; else Read_en <= 0; end always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) Data_send_reg <= 0; else if(Send_en == 1) Data_send_reg <= Data_send; else cnt_divide <= 0; end always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) cnt_divide <= 0; else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1) cnt_divide <= 0; else if(act_flag == 1) cnt_divide <= cnt_divide + 1"b1; else cnt_divide <= 0; end always @(posedge Clk or negedge Rst_n) begin//生成目标时钟两倍频率的的cnt_pulse if(Rst_n == 0) cnt_pulse <= 0; else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1 & cnt_pulse == 16) cnt_pulse <= 0; else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1) cnt_pulse <= cnt_pulse + 1"b1; else if(act_flag == 1) cnt_pulse <= cnt_pulse; else cnt_pulse <= 0; end always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) begin if(CPOL == 1) begin Spi_clk <= 1; Spi_mosi <= 1; Data_recive <= 0; end else begin Spi_clk <= 0; Spi_mosi <= 1; Data_recive <= 0; end end else if(cnt_divide == Value_divide/2 - 1 & act_flag == 1) begin if(CPHA == 0) case(cnt_pulse) 0:begin Spi_clk <= Spi_clk; Spi_mosi <= Data_send_reg[7]; Data_recive <= Data_recive; end 1:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[7] <= Spi_miso; end 2:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[6]; Data_recive <= Data_recive; end 3:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[6] <= Spi_miso; end 4:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[5]; Data_recive <= Data_recive; end 5:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[5] <= Spi_miso; end 6:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[4]; Data_recive <= Data_recive; end 7:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[4] <= Spi_miso; end 8:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[3]; Data_recive <= Data_recive; end 9:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[3] <= Spi_miso; end 10:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[2]; Data_recive <= Data_recive; end 11:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[2] <= Spi_miso; end 12:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[1]; Data_recive <= Data_recive; end 13:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[1] <= Spi_miso; end 14:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[0]; Data_recive <= Data_recive; end 15:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[0] <= Spi_miso; end 16:begin Spi_clk <= ~Spi_clk; Spi_mosi <= 1; Data_recive <= Data_recive; end default:; endcase else case(cnt_pulse) 0:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[7]; Data_recive <= Data_recive; end 1:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[7] <= Spi_miso; end 2:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[6]; Data_recive <= Data_recive; end 3:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[6] <= Spi_miso; end 4:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[5]; Data_recive <= Data_recive; end 5:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[5] <= Spi_miso; end 6:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[4]; Data_recive <= Data_recive; end 7:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[4] <= Spi_miso; end 8:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[3]; Data_recive <= Data_recive; end 9:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[3] <= Spi_miso; end 10:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[2]; Data_recive <= Data_recive; end 11:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[2] <= Spi_miso; end 12:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[1]; Data_recive <= Data_recive; end 13:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[1] <= Spi_miso; end 14:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Data_send_reg[0]; Data_recive <= Data_recive; end 15:begin Spi_clk <= ~Spi_clk; Spi_mosi <= Spi_mosi; Data_recive[0] <= Spi_miso; end 16:begin Spi_clk <= Spi_clk; Spi_mosi <= 1; Data_recive <= Data_recive; end default:; endcase end end assign Cs_output = CS_input; endmodule2、设计的模块

`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company: GDUT// Engineer: Lclone// // Create Date: 2023/01/23 22:12:11// Design Name: SPI_Bytes// Module Name: SPI_Bytes// Project Name: // Target Devices: // Tool Versions: // Description: // - 可以设置位1-128字节的SPI通信模块// - 可以修改CPOL、CPHA来进行不同的通信模式// - 可以设置输出的时钟// // Dependencies: // // Revision:// Revision 0.01 - File Created// Additional Comments:// //////////////////////////////////////////////////////////////////////////////////module SPI_Bytes# ( parameter Data_Width = 16, //数据位宽 parameter ROUNDS = Data_Width/8) //传输轮数(例化时不需要设置) ( //-----------------内部接口-------------------- input Clk, //时钟信号 input Rst_n, //复位信号 input [Data_Width-1:0] Send_Bytes_Data, //发送的多字节数据 input Bytes_Send_en, //多字节发送使能 output reg [Data_Width-1:0] Recive_Bytes_Data, //接收的多字节数据 output reg Bytes_Read_en, //多字节读使能 input Cs_input, //片选信号输入 //-----------------外部接口-------------------- output Spi_mosi, //主输出从输入 input Spi_miso, //主输入从输出 output Spi_clk, //输出时钟 output Cs_output //片选信号输出 ); reg send_en; //发送使能 wire read_en; //读使能 reg [7:0] data_send; //待发送数据 reg [Data_Width-1:0] Send_Bytes_Data_reg; //多字节数据寄存器 wire[7:0] data_recive; //接收的数据 reg [9:0] round; //发送次数(修改该位宽可改变最大发送数据位宽) reg [1:0] state; //状态寄存器 always @(posedge Clk or negedge Rst_n) begin if(Rst_n == 0) round <= 0; else if(round == ROUNDS) round <= 0; else if(read_en == 1) round <= round + 1"b1; else round <= round; end always @(posedge Clk or negedge Rst_n) begin//状态机 if(Rst_n == 0) begin state <= 0; Bytes_Read_en <= 0; data_send <= 0; Send_Bytes_Data_reg <= 0; send_en <= 0; Recive_Bytes_Data <= 0; end else case(state) 0://空闲状态 begin Bytes_Read_en <= 0; if(Bytes_Send_en == 1) begin state <= 1; Send_Bytes_Data_reg <= Send_Bytes_Data; end else state <= 0; end 1://发送状态 begin send_en <= 0; if(round == ROUNDS) begin state <= 0; Bytes_Read_en <= 1; Recive_Bytes_Data[7:0] <= data_recive;//由于发送和接收的时序略有不同,这里给接收做个补偿。 end else begin state <= 2; send_en <= 1; data_send <= Send_Bytes_Data_reg[Data_Width-1:Data_Width-8];//发送高位 Recive_Bytes_Data[7:0] <= data_recive;//把接收到的数据放在低位 end end 2://数据移位 begin send_en <= 0; if(read_en == 1) begin Send_Bytes_Data_reg <= Send_Bytes_Data_reg << 8;//高位刷新 Recive_Bytes_Data <= Recive_Bytes_Data << 8;//把低位的数据移到高位 state <= 1; end else state <= 2; end default:; endcase endSPI_Interface# ( .Value_divide (4)) //分频系数SPI_SPI_Interface_inst ( //-----------------内部接口------------------ .Clk (Clk), //时钟信号 .Rst_n (Rst_n), //复位信号 .CPOL (1), .CPHA (0), .CS_input (1), //片选输入 .Send_en (send_en), //发送使能 .Data_send (data_send), //待发送数据 .Read_en (read_en), //读使能 .Data_recive (data_recive), //接收的数据 //------------------外部接口------------------ .Spi_clk (Spi_clk), //输出时钟 .Spi_mosi (Spi_mosi), //主输出从输入 .Spi_miso (Spi_miso), //主输入从输出 .Cs_output (Cs_output) //片选输出 );endmodule二、仿真

1、仿真激励

`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company: // Engineer: // // Create Date: 2023/01/26 16:00:48// Design Name: // Module Name: SPI_Bytes_tb// Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision:// Revision 0.01 - File Created// Additional Comments:// //////////////////////////////////////////////////////////////////////////////////module SPI_Bytes_tb(); reg clk_50m;initial clk_50m <= 1;always #10 clk_50m <= ~clk_50m; reg rst_n;initial begin rst_n <= 0; #200 rst_n <= 1;end reg Bytes_Send_en;reg [31:0] Send_Bytes_Data;wire Bytes_Read_en;wire [31:0] Recive_Bytes_Data;wire Spi_clk;wire Spi_mosi;wire Spi_miso;wire Cs_output; SPI_Bytes# ( .Data_Width (32))//数据位宽为32位SPI_Bytes_inst ( //-----------------内部接口-------------------- .Clk (clk_50m), .Rst_n (rst_n), .Send_Bytes_Data (Send_Bytes_Data), .Bytes_Send_en (Bytes_Send_en), .Recive_Bytes_Data (Recive_Bytes_Data), .Bytes_Read_en (Bytes_Read_en), .Cs_input (1"b1), //-----------------外部接口-------------------- .Spi_mosi (Spi_mosi), .Spi_miso (Spi_miso), .Spi_clk (Spi_clk), .Cs_output (Cs_output) ); assign Spi_miso = Spi_mosi; initial begin Bytes_Send_en <= 0; Send_Bytes_Data <= 0; #400; Bytes_Send_en <= 1; Send_Bytes_Data <= 32"h89abcdef; #20 Bytes_Send_en <= 0; #4000; Bytes_Send_en <= 1; Send_Bytes_Data <= 32"h12345678; #20 Bytes_Send_en <= 0;end endmodule2、仿真结果

仿真结果:两次多字节发送都能正确的发送和接收数据,且能正确的生成Bytes_Read_en信号。模块仿真验证可行。

-

-

-

-

每日简讯:用状态机实现通用多字节SPI接口模块

世界播报:满江红票房破21亿!张艺谋揭秘震撼结尾 片方发声明称偷票房等指责纯属造谣

天天简讯:辽宁上空惊现“三个太阳”幻日奇观 手机拍下罕见一幕:专家揭秘成因

数字签名技术

当前滚动:小朋友哈尔滨室外舔冰雕舌头被粘:东北的冰真的是甜的吗?

环球热议:信号大升级!iPhone 15系列有望支持Wi-Fi 6E传输标准

今热点:实现有序表的增删改查

世界最资讯丨核显的春天来了!SK海力士发布最快LPDDR5T内存:飙上9.6Gbps

每日看点!明年再见!充电器一拔我和浪浪山道别了引热议 专家建议春节假期延至9天

东南亚赚大:中国游客彻底抛弃日本、韩国 这波打击影响太惨

全球速看:一家5人花100块去看“时空隧道” 直言开心就值:网友调侃参观蔬菜大棚

京东最便宜2TB SSD秒杀:569元还是TLC颗粒

世界新消息丨票房超19亿!网友质疑《满江红》剧情抄袭《龙门镖局》 10年前梗都照搬

全球头条:日本公司推出懒人沙发:走哪躺哪

环球滚动:还要更便宜!特斯拉:近5年车辆平均售价已减半 将继续控制成本

环球热消息:新增万名雇员!2022年荷兰半导体巨头ASML营收破纪录

【快播报】驾驶辅助技能大比拼 特斯拉殿后

天天看点:【个人笔记】2023年搭建基于webpack5与typescript的react项目

获11年来最大营收增幅照裁不误:IBM宣布将裁员3900人

世界快讯:苹果官网开售Mac Studio“锁具套装”:一个密码锁卖到548元

世界观察:为啥特斯拉疯狂降价到20多万 利润依然最高?官方揭秘真相

焦点!三星Galaxy S23 Ultra拍摄样张流露:30X变焦效果比S22 Ultra 20X更清晰

微速讯:RTX 4060将至:TGP功耗160W 可能采用传统8PIN供电

重点聚焦!影院回应《流浪地球2》改播《满江红》引热议:设备故障不能放

天天视点!全球数万用户遭波及:微软终于修复OneDrive等服务宕机问题

快资讯:Intel新款锐炫显卡现身:16 Xe核心 比A770弱42%

环球滚动:读Java8函数式编程笔记01_Lambda表达式

快资讯丨你为啥还不升级Win11?微软:1月31日停售Windows 10

世界速递!腾讯NVIDIA达成深度合作:打造低延迟超大分辨率渲染平台

当前视点!手机Galaxy S23系列手机保护壳曝光:独占功能 可滑动解锁

win11启动虚拟机出现蓝屏

全球聚焦:女子零下14度观影被冻到扶墙退场 网友:这是5D电影 身临其境

天天视讯!2023春节档总票房突破50亿!有望冲击史上最强春节档

世界短讯!向Redmi Note 12 Pro极速版看齐!小米Poco X5 Pro即将发布:骁龙778G配1亿像素主摄

世界热消息:安徽一电竞酒店装30块RTX 4090显卡:梦幻装备 玩了回不去

看热讯:Dart常用核心知识

世界热讯:带薪撸猫 女子过年不回家搞副业十天赚几千

编程与类型系统读后总结与感想

MySQL数据库

全球快资讯:国产新型量子计算机即将发布 中国第一家量子计算公司打造

短讯!《流浪地球2》智能机械狗“笨笨”开售:899元 支持遥控

每日信息:vue-grid-layout数据可视化图表面板优化过程所遇问题汇总

焦点讯息:索尼再次动刀!宣布电视、相机等产品即将涨价14%

全球实时:魅族20外观设计现身:极窄直屏边框颜值在线

头条:回文数-力扣

每日看点!蔚来车主占三个车位充电引争议 汽车博主:好像只能这么充

男孩打开新年礼盒发现是试卷后大哭:寒假作业还没有写完

天天视讯!漠河零下53℃极寒 有居民屋里穿短袖!网友集体羡慕:我们这取暖靠抖

当前快播:2022年度中国汽车保值率:日系车屠榜 秒杀BBA豪华车

学习笔记——NoSQL数据库;Redis概述;redis中常用的数据类型(key、string)

环球热头条丨比亚迪或进军保险业 将全资接盘易安财险

春运时间翻倍!电动车车主称油车返乡8小时 他开了15小时

每日视讯:《满江红》票房逆跌 成春节档冠军!张艺谋刷新个人纪录

天天速讯:海外观众评价《流浪地球2》:不比《星际穿越》差

速度高达9.6Gbps!SK海力士发布全球最快移动DRAM

世卫组织:全球50亿人无法避免反式脂肪 会致命的有毒化学物质

在家享受牛奶SPA!舒蕾沐浴露大促:10元/斤

世界头条:马斯克或参与特斯拉自动驾驶视频造假?细节曝光

观速讯丨微软裁员1万人 遣散费高达8亿美元 平均每人获赔54万元

MiniLED国货崛起?2023年的电视不太好下手

iPhone 15 Pro相机将迎来质变:5倍潜望长焦赶上安卓阵营

2023春节档票房破40亿!《满江红》14亿票房领跑

环球播报:吃饺子就是得蘸醋 这件事在几亿年前就决定了!

每日观察!印度收到90亿光年外星系无线电信号 天文学家:外星人没有参与

复旦教授:《流浪地球2》不输于近5年任何一部国外科幻大片

天天观速讯丨27年前 中国自研第一台64位超级小型计算机 当时世界最先进

【天天报资讯】《流浪地球2》:当一部电影演到第三个钟头

谁说中国人造不出保时捷?

今日视点:RTX 4090依旧掉帧!SE大作《Forspoken》今日发售:成新一代硬件杀手

全球今日报丨全球汽车畅销榜:美国忠爱大皮卡 国人狂买比亚迪

什么是闭包?

全球新动态:猫咪机器人下国际象棋快逼疯人类 顶级棋手也只能和它打成平局

【天天播资讯】薛之谦发文告别暴雪 自称“曲阳爆叉叉兵一波流王”

mac的m芯片安装gup版本的pytroch,并链接到pycharm

泰山温度-22℃ 游客大雪中抱团 网友感叹:还以为翻拍《长津湖》

每日观点:雷军告别《魔兽世界》:18年前就玩了 感慨万千 再见艾泽拉斯

兔年邮票为啥是蓝色兔子?设计者女儿说出真相

世界速讯:中国影史首个!吴京个人总票房达300亿

一加首款机械键盘来了:水晶旋钮 无小数字键

世界视点!python简单实现对桌面进行实时捕捉画面

小米汽车前脸设计图疯传 王化回应:早期招标设计稿 并非最终版

全球热点!女子吐槽羽绒服到东北变嘎嘣脆 为什么遇冷会变硬?

世界实时:学习笔记——Linux中搜索查找类命令;压缩和解压类;Linux挂载和卸载;进程线程类命令;RPM;YUM

环球热消息:太假了!网友分析《三体》动画B站真实评分为2.1分

焦点速递!《流浪地球2》TC版已流出 官博呼吁大家抵制盗版:文明观影

2023牛客寒假算法基础集训营1 个人题解(ACDHKL)

每日看点!大过年的临时工玩呢 AMD又搞了个乌龙:锐龙7000X3D不能超频

天天简讯:彻底离开中国制造不现实 未来苹果将有25%产品来自印度

世界关注:“终极功率半导体”获突破性进展!金刚石有望成为终极半导体材料

每日动态!NASA第一架电动飞机即将上天 官宣至今已过去7年

世界实时:全球最高安全标准 我国自研第三代核电华龙一号稳步推进:1台年发电100亿度

环球今日报丨学习笔记——CentOS中的时间日期类命令;用户管理类命令(useradd,passwd ,id,su ,userdel,who ,usermod,

天天日报丨RTX 4060 Ti性能、价格逼近RTX 3070 网友质疑:升级图啥

steam春节特卖:11款热卖大作 部分游戏低至2折

读函数式编程思维笔记05_现实应用

每日热点:学习笔记——CentOS中的帮助命令;常用快捷键;文件目录类命令

全球视点!猪肉没有以前香了 我们的餐桌已被洋猪肉占据 鲜香早已不复当年

天天亮点!马斯克为“特斯拉私有化推文案”辩护:本可通过出售SpaceX的股份完成融资

环球快报:阿里云盘TV版上线 电视上直接看网盘里的大片

中科院研发新一代“电力银行”:充满可供20万人用一天